SAM E54 pin Function Ethernet function Shared functionality

PD12 GPIO INTERRUPT

PC21 GPIO RESET

The KSZ8091RNACA also has a set of parameters that are latched in during reset based on I/O pin

levels. These configuration options have a default mode on the kit done by external pull-up and pull-down

resistors. For detailed information about the configuration, see the KSZ8091RNACA datasheet.

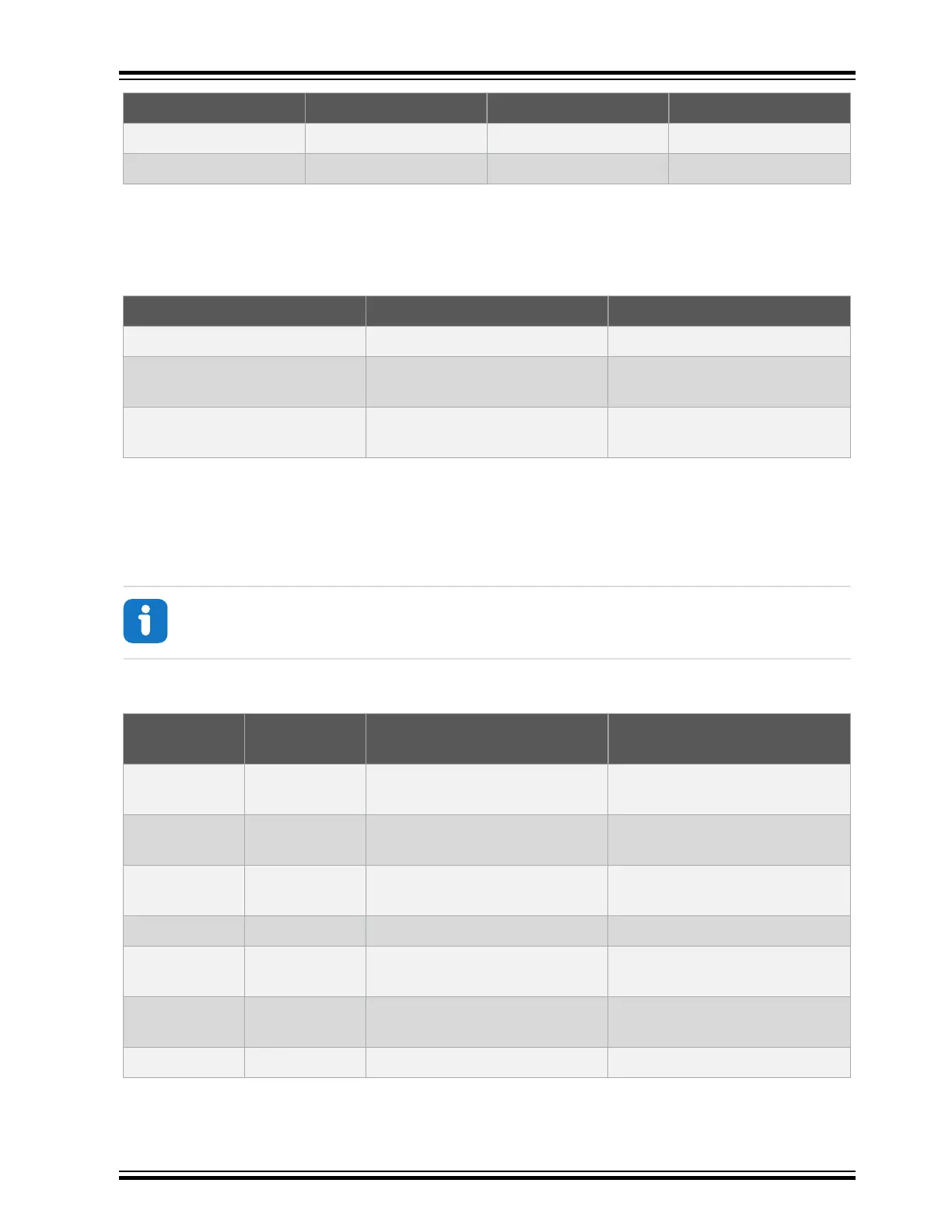

Table 5-19. KSZ8091RNACA Kit Configuration

Configuration name Default value on kit Default configuration

PHYAD 00 The PHYs address is 00000

PME_EN 0 Disable PME Enable output for

Wake-On-LAN

ANEN_SPEED 1 Auto negotiation enabled and

100Mbps link speed enabled

5.3.8 AT24MAC402

SAM E54 Xplained Pro features one external AT24MAC402 serial EEPROM with a EIA-48 MAC address

connected to the SAM E54 through I

2

C. This device contain a MAC address for use with the Ethernet

interface. The table below lists all I/O-lines connected to the ATMAC402 device.

Info: The I

2

C EEPROM address is 0x56 and extended address is 0x5E (7-bit, right adjusted

without R/W bit).

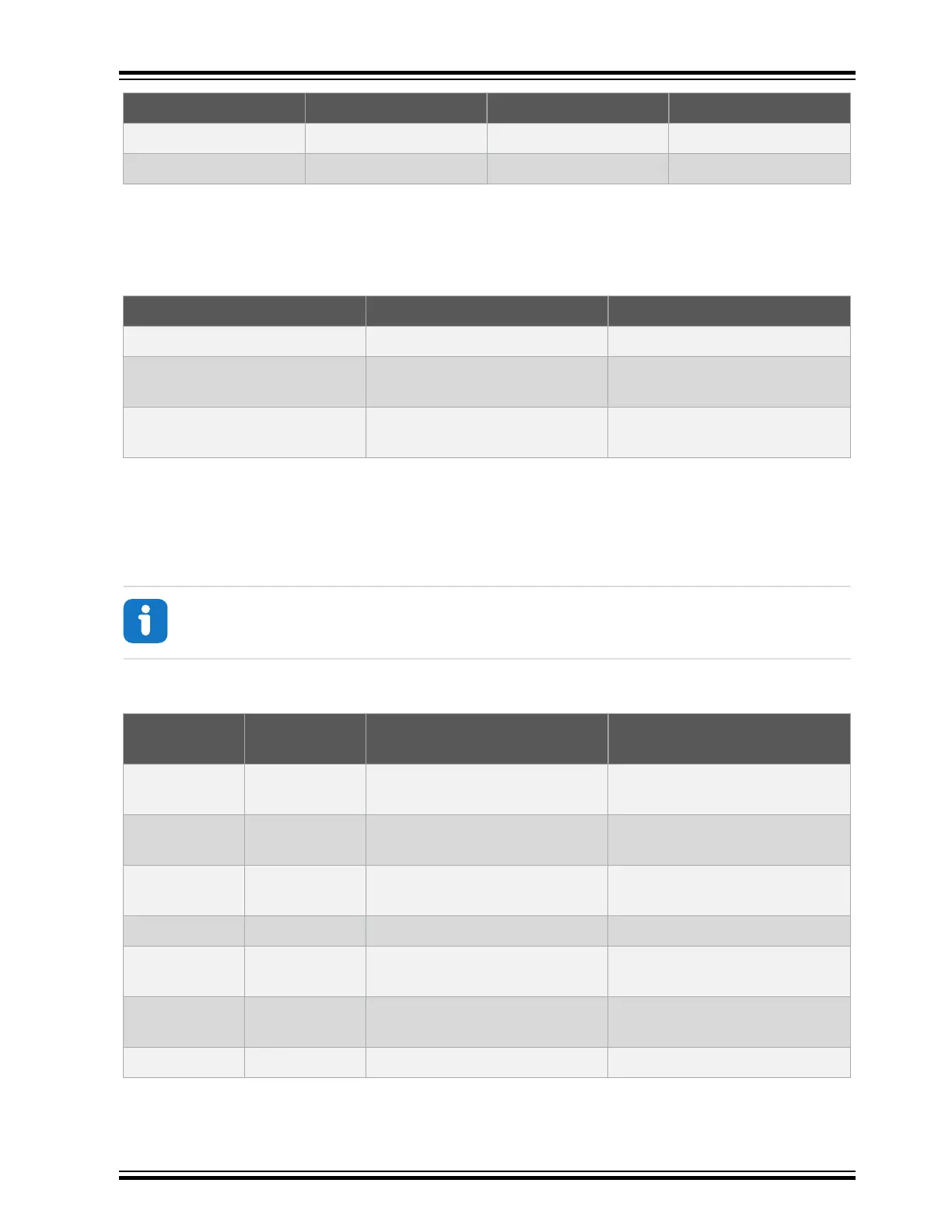

Table 5-20. AT24MAC402 Connections

AT24MAC402

pin

SAM E54 pin Function Shared functionality

1 [A0] - Address bit 0 config (Pulled to

GND)

-

2 [A1] - Address bit 1 config (Pulled to

VCC)

-

3 [A2] - Address bit 2 config (Pulled to

VCC)

-

4 [GND] - GND -

5 [SDA] PD08 SERCOM7 PAD[0] I

2

C SDA ATECC508, PCC, EXT2, EXT3,

and EDBG DGI

6 [SCL] PD09 SERCOM7 PAD[1] I

2

C SCL ATECC508, PCC, EXT2, EXT3,

and EDBG DGI

7 [WP] - Write Protect (Pulled to GND) -

SAM E54 Xplained Pro

© 2017 Microchip Technology Inc.

DS70005321A-page 27

Loading...

Loading...