Info: Note that there are some resistors that aren't mounted by default on the kit listed in the

table below.

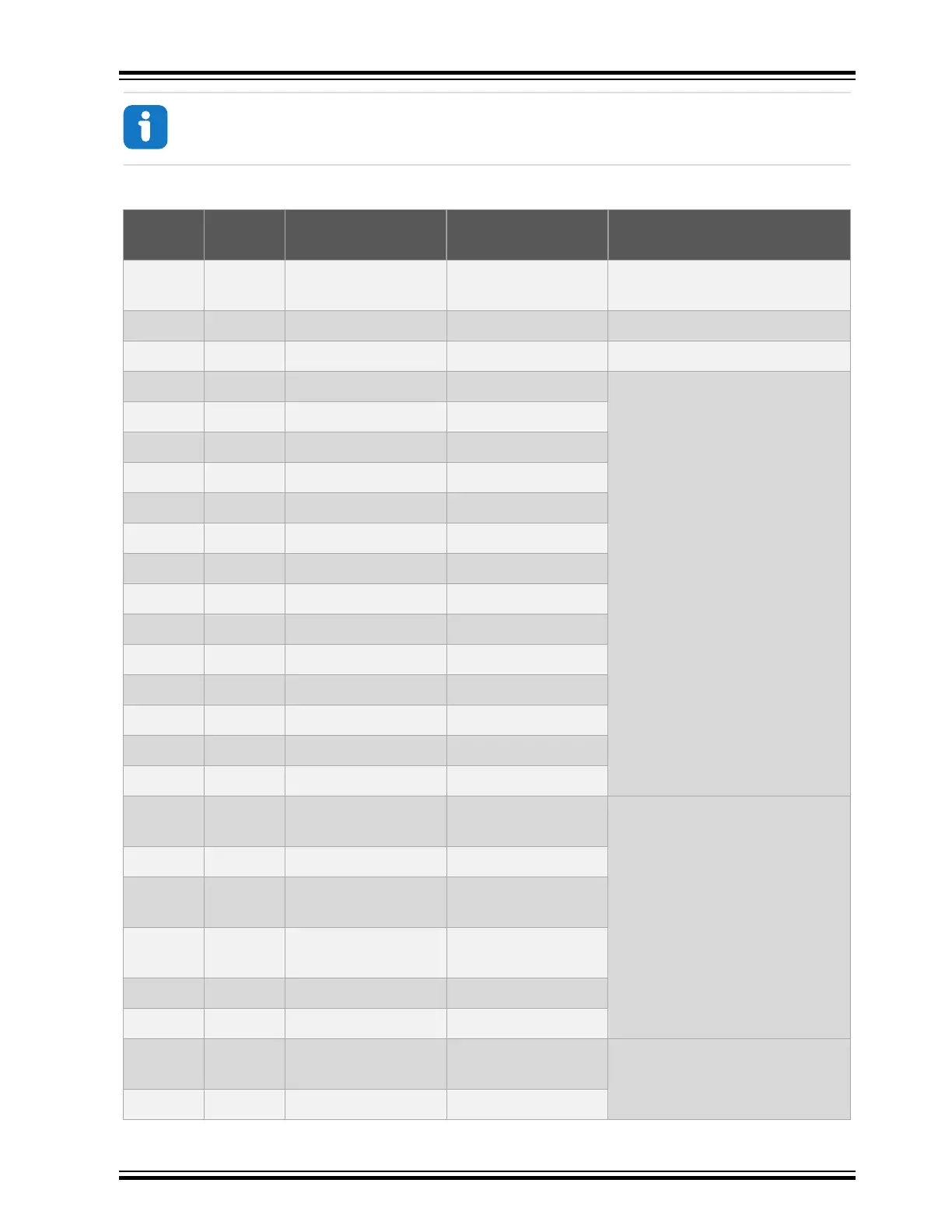

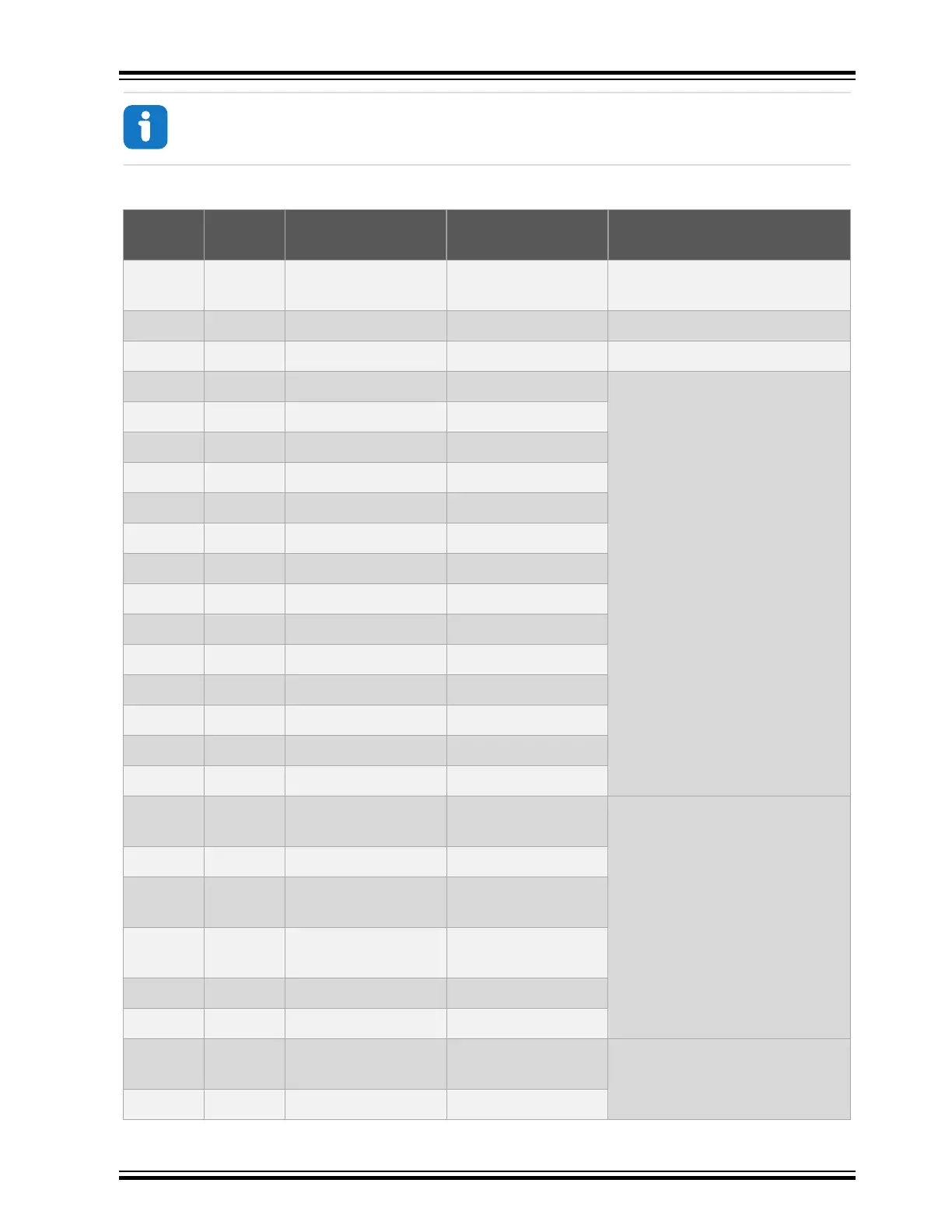

Table 5-29. Resistors

Designat

or

Value From To Comment

J101 cut-strap VCC_P3V3 VCC_P3V3_CM_IN ATSAME54P20A, peripherals

and connectors power supply

R101 0Ω U100 OUT VCC_CM_P3V3 XAM power supply

R103 0Ω U100 OUT VCC_EDBG_P3V3 EDBG power supply

R205 0Ω [N.M.] J406 PCC DATA04 PA20 SDHC CMD Allows complete or partial

disconnect of header J406,

Parallel Capture Controller,

header from ATSAME54P20A,

and shared signals. Remove the

mounted resistors and mount the

unmounted resistors if using the

PCC header.

R206 0Ω [N.M.] J406 PCC DATA05 PA21 SHDC CK

R207 0Ω [N.M.] J406 PCC DATA06 PA22 I

2

C HS SDA

R208 0Ω [N.M.] J406 PCC DATA07 PA23 I

2

C HS SCL

R308 10kΩ PCC DATA0 QTouch Button

R621 0Ω PA17 ETH GTXEN PHY_TXEN

R622 0Ω PA18 ETH GTX0 PHY_TXD0

R623 0Ω PA19 ETH GTX1 PHY_TXD1

R624 0Ω PA13 ETH GRX0 PHY_RXD0

R625 0Ω PA12 ETH GRX1 PHY_RXD1

R626 0Ω PA15 ETH GRXER PHY_RXER

R628 0Ω PC12 ETH GMDIO PHY_MDIO

R629 0Ω PC11 ETH GMDC PHY_MDC

R630 0Ω PA14 ETH GTXCK PHY_REFCLK

R609 4.7kΩ

[N.M.]

PHYAD VCC_TARGET_P3V3 Configuration for default start-up

conditions for the Ethernet PHY.

R616 1kΩ PHYAD GND

R613 4.7kΩ

[N.M.]

PME_EN VCC_TARGET_P3V3

R618 1kΩ

[N.M.]

PME_EN GND

R605 4.7kΩ ANEN_SPEED VCC_TARGET_P3V3

R619 1kΩ ANEN_SPEED GND

R802 39Ω EDBG TARGET

RESET

TARGET MCU

RESET

Debug interface from the EDBG

to the ATSAME54P20A

R803 0Ω EDBG SWCLK PA30 SWCLK

SAM E54 Xplained Pro

© 2017 Microchip Technology Inc.

DS70005321A-page 33

Loading...

Loading...