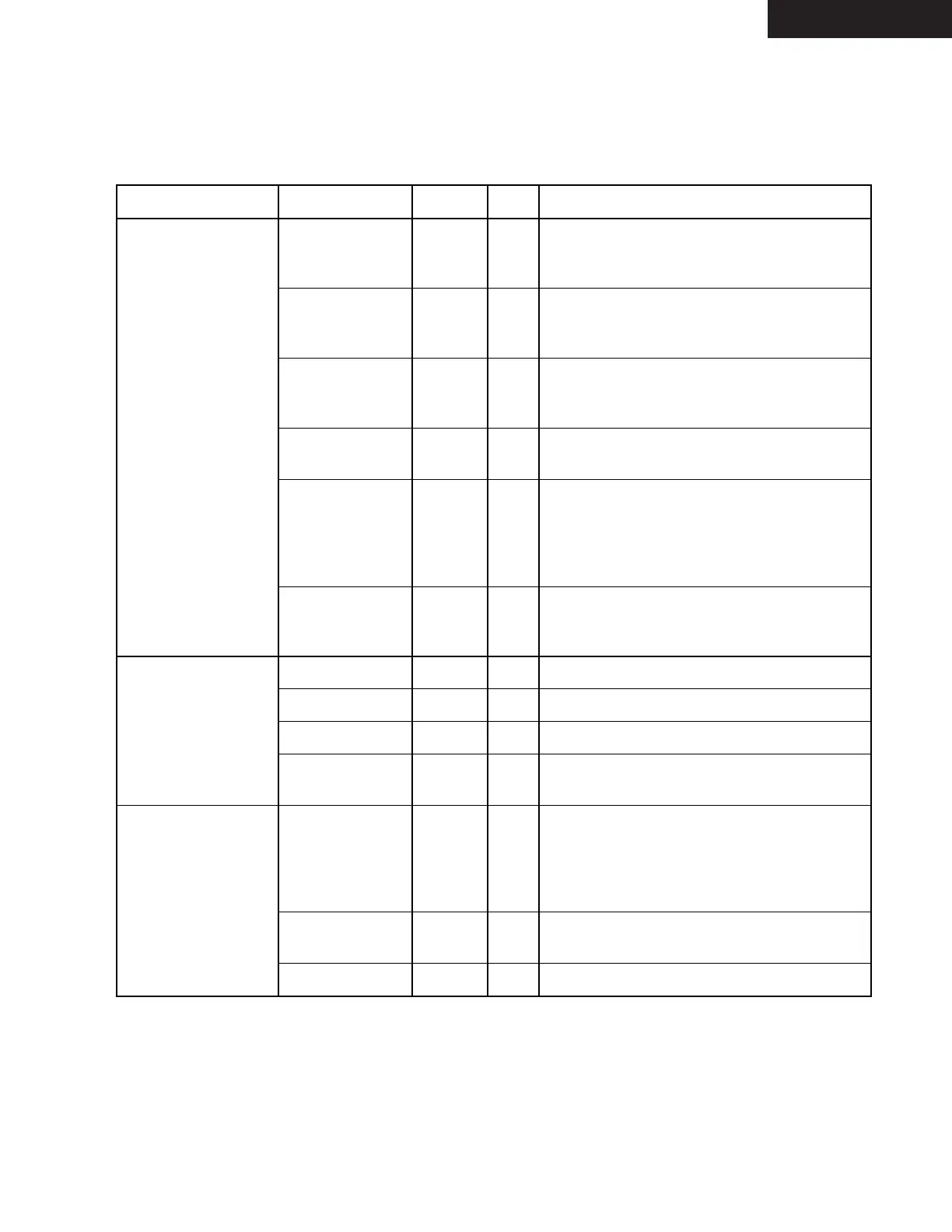

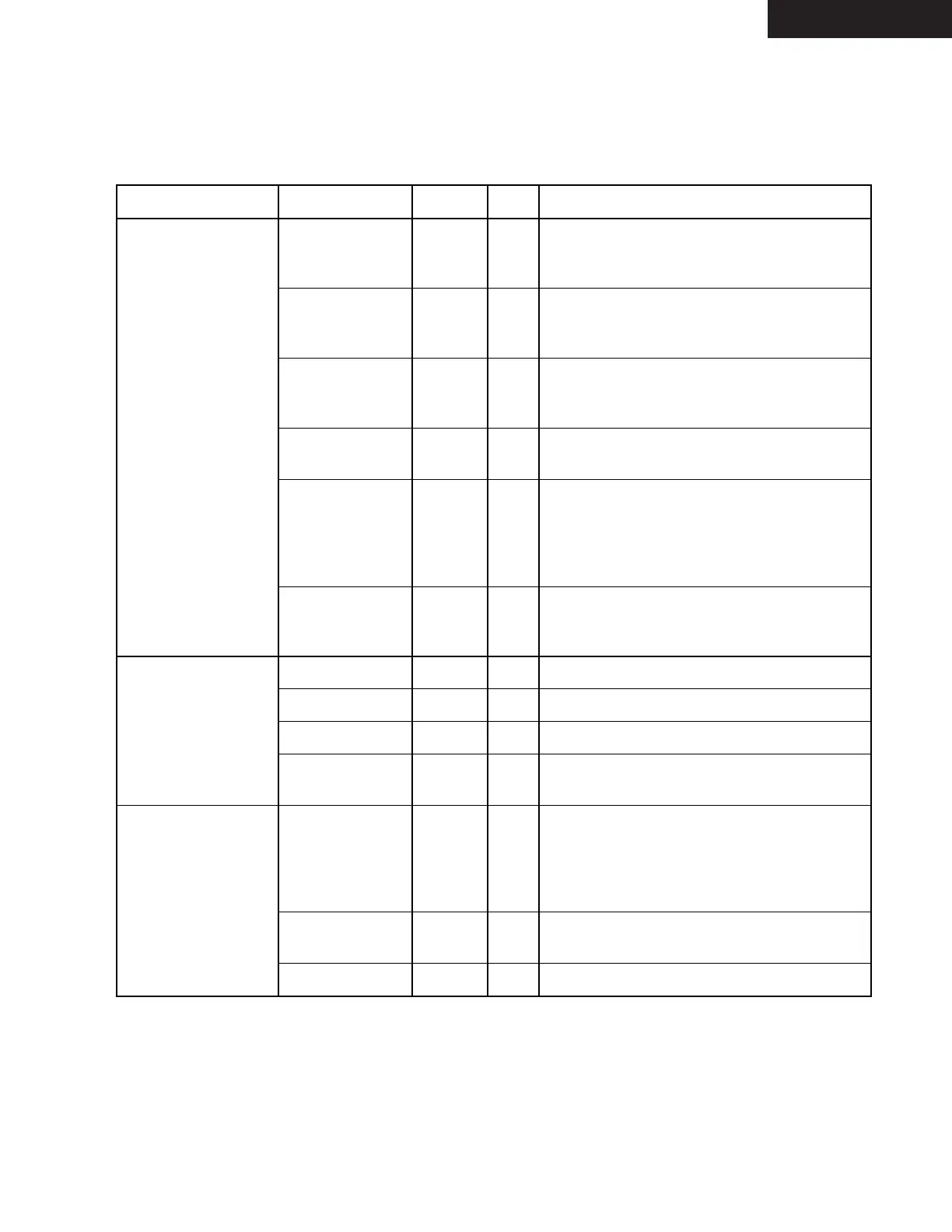

IC BLOCK DIAGRAMS AND TERMINAL DESCRIPTIONS -34

Q8001 : SII504 (I/P Video Converter)

TX-SR674/674E/8467

Signal Group

Signal Name

Notes

Type

Description

Host Interface HostData[15:8] 5V/PD InOut 186-Compatible Data when HostMode = 0.

(continued) (VidInData[19:2]) Chroma video input data (16-bit & H/V syncs

format) when HostMode = 1.

HostData[7] 5V/PD InOut 186-Compatible Data when HostMode = 0.

(VS) Vertical sync input (8/16-bit & H/V syncs

format) when HostMode = 1.

HostData[6] 5V/PD InOut 186-Compatible Data when HostMode = 0.

(HS) Horizontal sync input (8/16-bit & H/V syncs

format) when HostMode = 1.

HostData[5:0] 5V/PD InOut 186-Compatible Data when HostMode = 0.

No connnect when HostMode = 1.

HostClk 5V InOut 186-Compatible Clock (33.33 MHz max) when

HostMode = 0. No Connect (27.0 MHz,

InOut) when HostMode = 1. Note that when

HostMode= 1, the clock output on HostClk

is also received and used internally.

HostMode 5V/PU In Serial Host Interface when HostMode = 1

(internal pullup defaults to this mode). 186-

compatible host interface when HostMode = 0.

Video Processing /Det32PD Out

3:2 Pulldown Sequence Detected.

Status /Det22PD Out

2:2 Pulldown Sequence Detected.

/DetVideo Out

Interlaced Video Sequence Detected.

/DeintDone Out Deinterlace processing complete for current

field period. Opendrain output.

External APLL /ExtRefSel 5V/PU In External APLL Reference Select. Internal

Reference Clock pullup defaults pin to a 1, selecting VidInClk

as the APLL reference clock. To select

ExtRefXtalIn as the APLL reference clock,

set /ExtRefSel to a 0.

ExtRefXtalIn In External APLL Reference Crystal/oscillator

Input.

ExtRefXtalOut Out External APLL Reference Crystal Output.

TERMINAL DESCRIPTION (4/5)

Loading...

Loading...