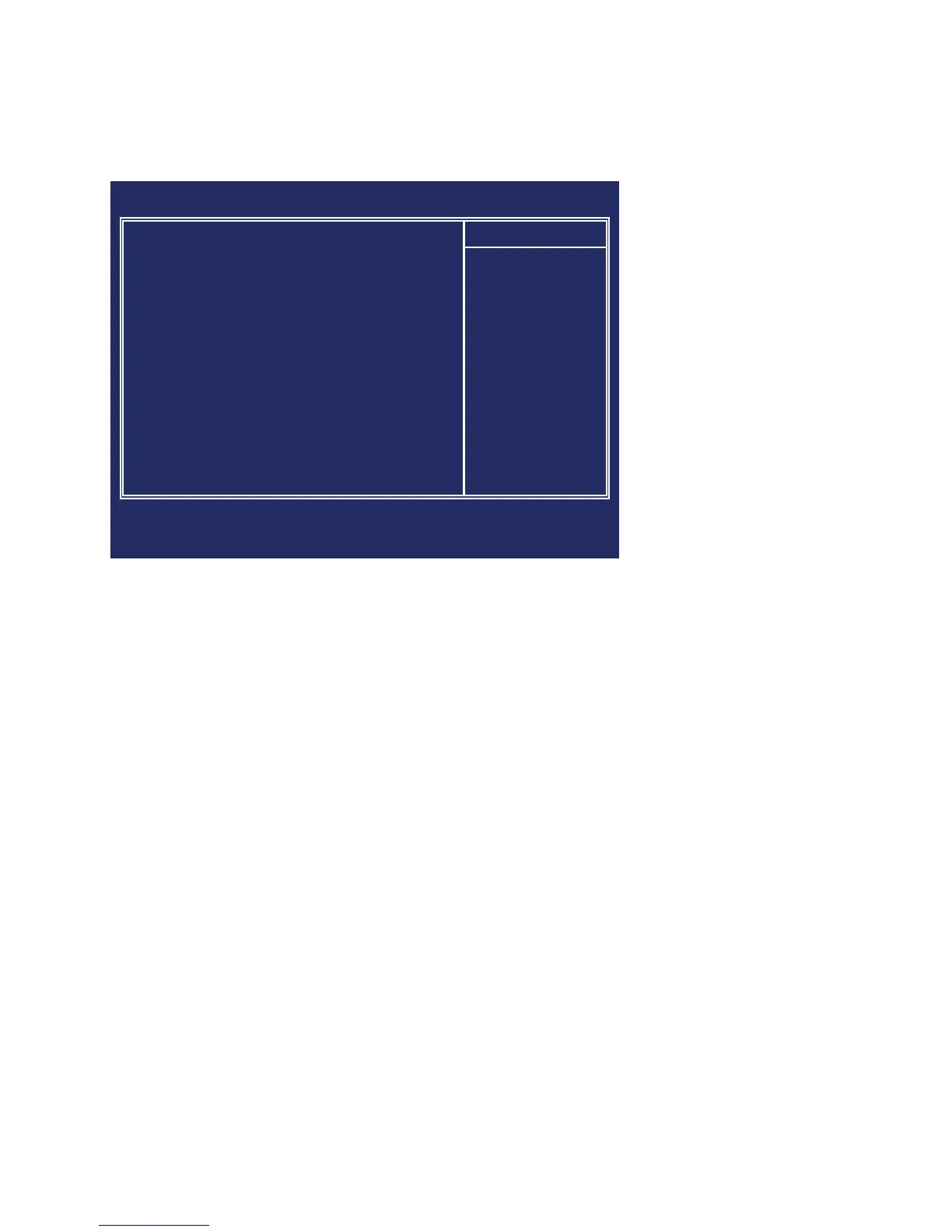

Advanced Chipset Features

This option displays critical timing parameters of the mainboard. Leave the items on this menu at their default

settings unless you are very familiar with the technical specications of the system hardware. If you change

the values incorrectly, you may introduce fatal errors or recurring instability into the system.

Advanced Figure 2.5

Chipset Features menu

Phoenix - AwardBIOS CMOS Setup Utility

Advanced Chipset Features

DRAM Timing Selectable By SPD x

CAS Latency Time 2.5 x

Active to Precharge Delay 7 x

DRAM RAS# to CAS# Delay 3 x

DRAM RAS# Precharge 3 x

DRAM Data Integrity Mode Non-ECC

System BIOS Cacheable [Enabled]

Video BIOS Cacheable [Enabled]

Memory Hole At 15M-16M [Disabled]

Delayed Transaction [Enabled]

Delay Prior to Thermal [16 Min]

AGP Aperture Size (MB) [64]

** On-Chip VGA Setting **

On-Chip Frame Buffer Size [16MB]

Item Help

↑↓→←:Move Enter:Select +/-/PU/PD:Value F10:Save ESC:Exit F1:General Help

F5:Previous Values F6:Fail-Safe Defaults F7:Optimized Defaults

DRAM Timing Selectable

Set this to the default value to enable the system to automatically set the SDRAM timing by SPD (Serial

Presence Detect). SPD is an EEPROM chip on the DIMM module that stores information about the memory

chips it contains, including size, speed, voltage, row and column addresses, and manufacturer. The default

value is By SPD.

CAS Latency Time

When the DRAM Timing Selectable is set to [Manual], this eld is adjustable. When synchronous DRAM is

installed, the number of clock cycles of CAS latency depends on the DRAM timing. The default value is 2.5.

Active to Precharge

When the DRAM Timing Selectable is set to [Manual], this eld is adjustable. This item controls the number

of cycles for Row Address Strobe (RAS) to be allowed to precharge. If insufcient time is allowed for the

RAS to accumulate its charge before DRAM refresh, refresh may be incomplete and DRAM may fail to retain

data. This item applies only when synchronous DRAM is installed in the system. The default value is 7.

DRAM RAS# to CAS# Delay

When the DRAM Timing Selectable is set to [Manual], this eld is adjustable. This eld lets you insert

a timing delay between the CAS and RAS strobe signals, used when DRAM is written to, read from, or

refreshed. Fast gives faster performance; and Slow gives more stable performance. This eld applies only

when synchronous DRAM is installed in the system. The default value is 3.

DRAM RAS# Precharge

When the DRAM Timing Selectable is set to [Manual], this eld is adjustable. This setting controls the

number of cycles for Row Address Strobe (RAS) to be allowed to precharge. If insufcient time is allowed

for the RAS to accumulate its charge before DRAM refresh, refresh may be incomplete and DRAM may fail

to retain data. This item applies only when synchronous DRAM is installed in the system. The default value

is 3.

DRAM Data Integrity Mode

Loading...

Loading...