5G Module Series

5G EVB User Guide

5G_EVB_User_Guide 26 / 36

3.8. UART Interfaces (J2003/J2002)

The 5G EVB supports two UART interfaces: main UART J2003 and debug UART J2002.

The main UART interface is used for communication between the module and the host application.

The debug UART interface J2002 is used for Linux console and log output, and supports baud rate of

115200 bps (default).

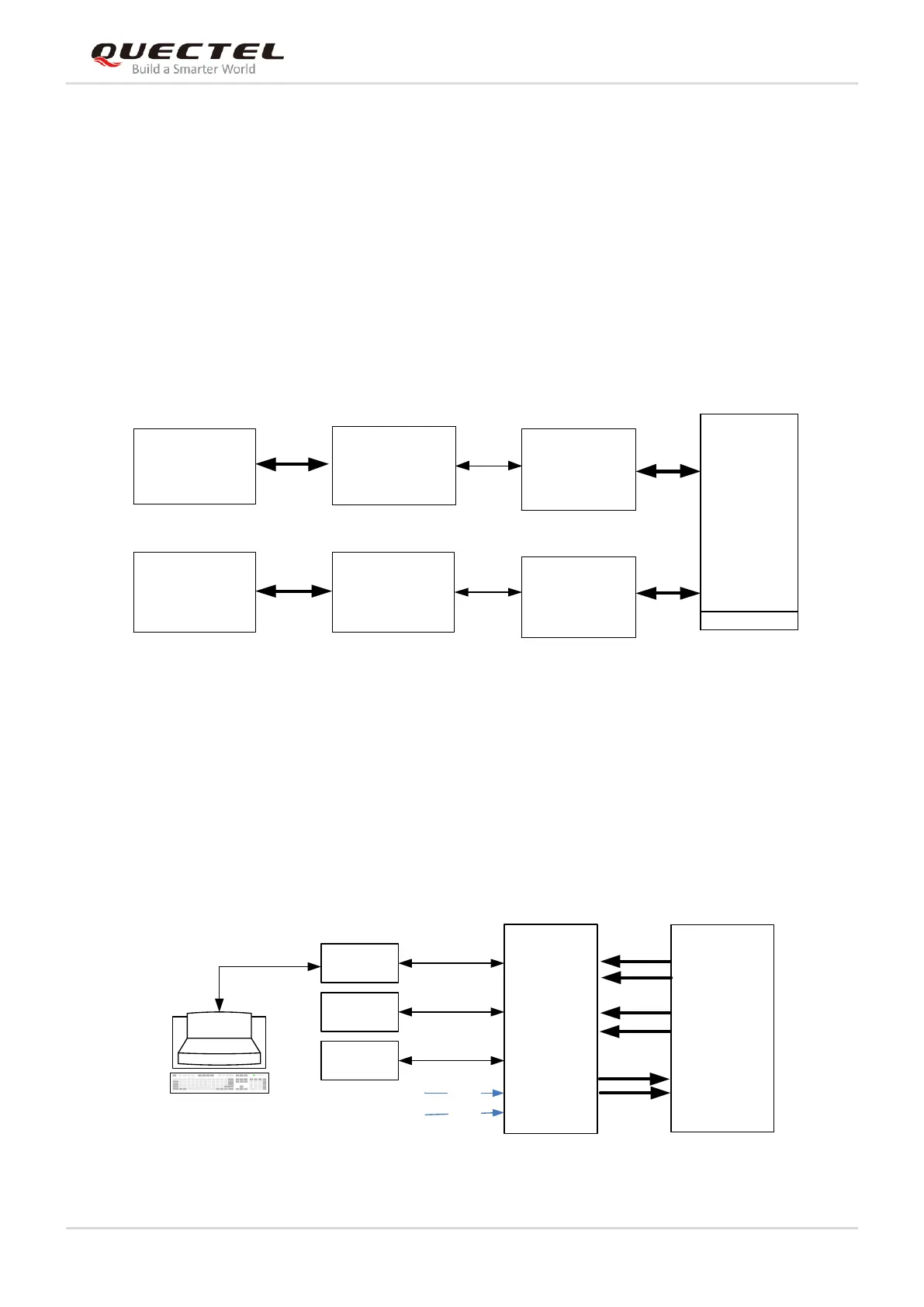

The following figure shows a block diagram of UART interfaces of the EVB.

Figure 19: UART Block Diagram

3.9. PCIe to USB Interface (J1601)

The 5G EVB reserves a PCIe 3.0 signal over USB interface for developers’ testing, and this function is not

enabled by default. Please refer to the following block diagram.

Loading...

Loading...