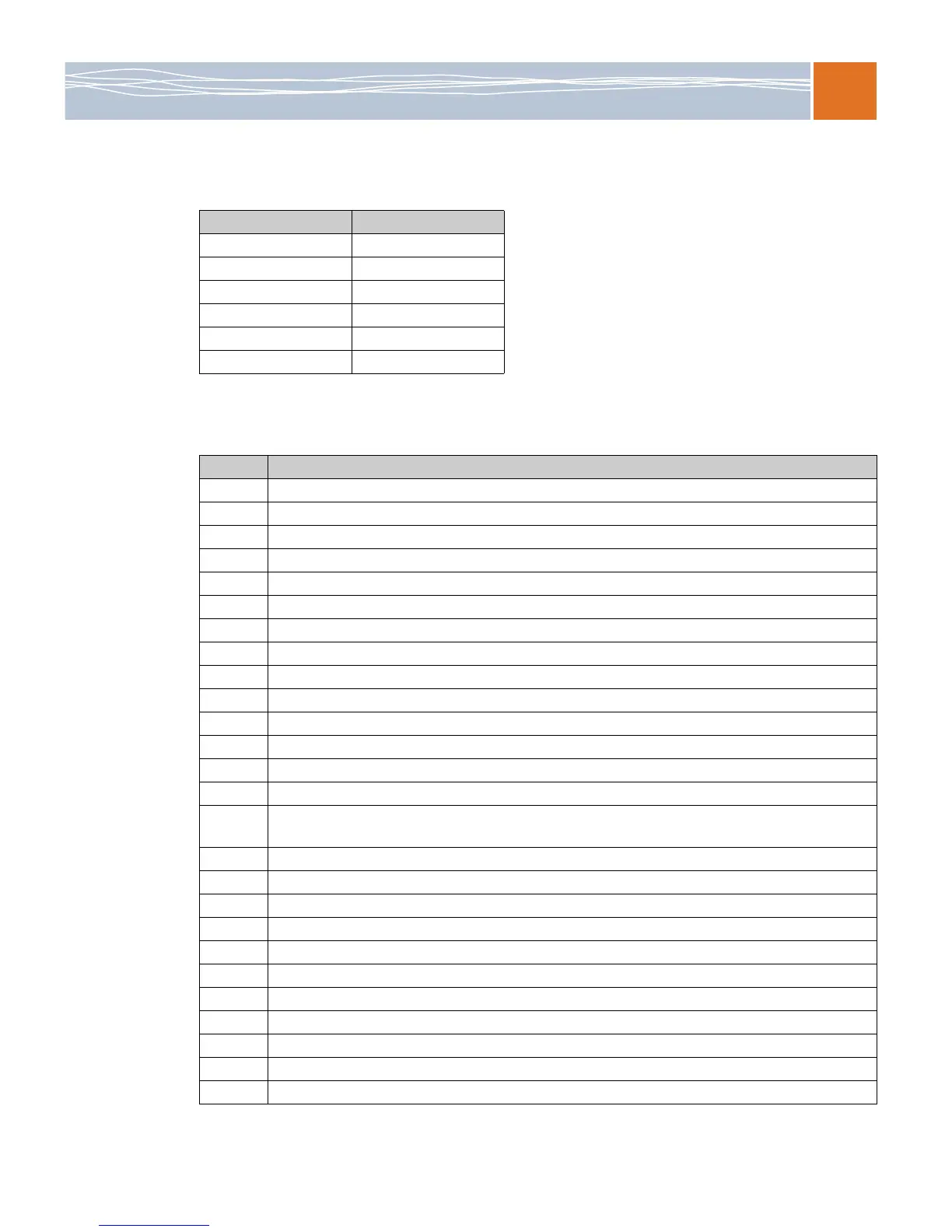

SMBus resource allocation

61

SMBus resource allocation

ISA interrupt allocation

Device Address

ICS 9LPR S511 1101001X

DIMM 0 Slot 10100000

DIMM 1 Slot 10100010

DIMM 2 Slot 10100100

DIMM 3 Slot 10101000

SIO H/W Monitor 01011010

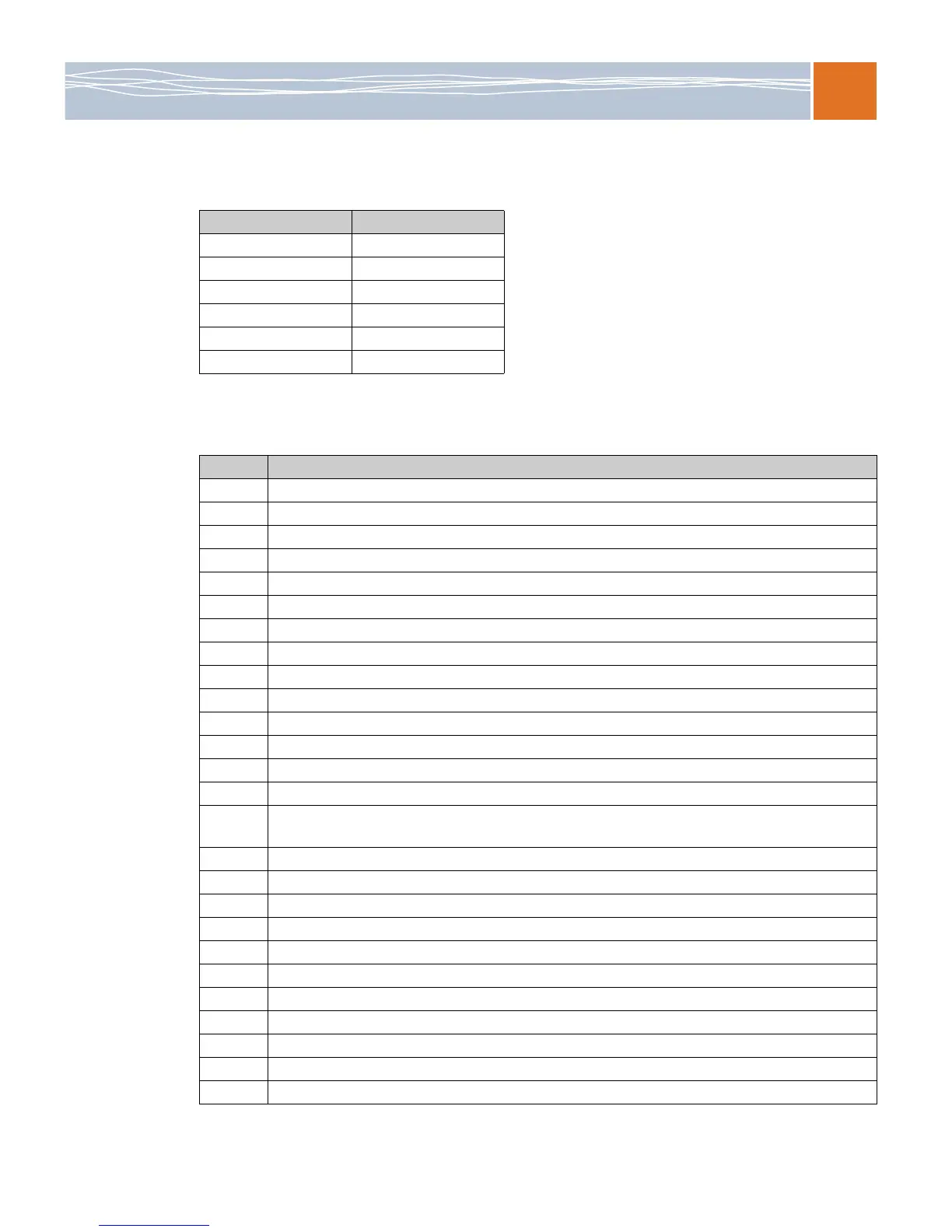

Interrupt Function

IRQ0 System timer (internal ICH7-M connection)

IRQ1 Keyboard controller via SERIRQ

IRQ2 Cascade interrupt input (internal ICH7-M connection)

IRQ3 COM2 via SERIRQ, PIRQ#

IRQ4 COM1 via SERIRQ, PIRQ#

IRQ5 PCI pool

IRQ6 PCI pool

IRQ7 PCI pool

IRQ8 RTC

IRQ9 PCI pool/Option for SCI, TCO

IRQ10 PCI pool/Option for SCI, TCO

IRQ11 PCI pool/Option for SCI, TCO

IRQ12 PS/2 mouse (if present and enabled)

IRQ13 Numeric coprocessor ~FERR (internal ICH7-M connection)

IRQ14 IDEIRQ (legacy mode, non-combined or combined mapped as primary), SATA primary (legacy

mode)

IRQ15 IDEIRQ (legacy mode, combined, mapped as secondary), SATA secondary (legacy mode)

NMI ICH7-M when ~SERR or ~IOCHK is asserted (software controlled)

SMI System management interrupt

PIRQA Internal devices are routable

PIRQB Internal devices are routable

PIRQC Internal devices are routable

PIRQD Internal devices are routable

PIRQE Option for SCI, TCO, HPET#0, 1, 2; other internal devices are routable

PIRQF Option for SCI, TCO, HPET#0, 1, 2; other internal devices are routable

PIRQG Option for SCI, TCO, HPET#0, 1, 2; other internal devices are routable

PIRQH Option for SCI, TCO, HPET#0, 1, 2; other internal devices are routable

Loading...

Loading...