System resources

68

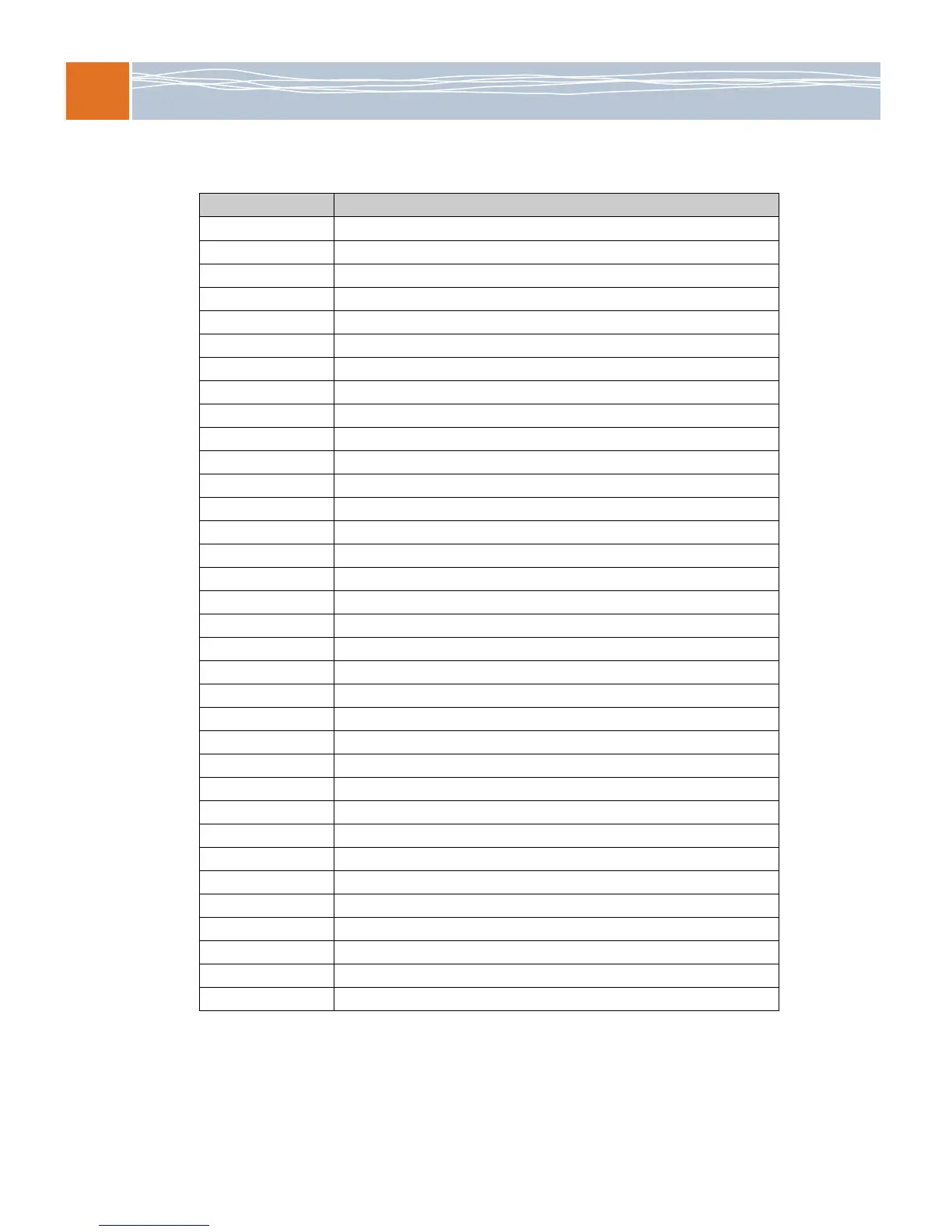

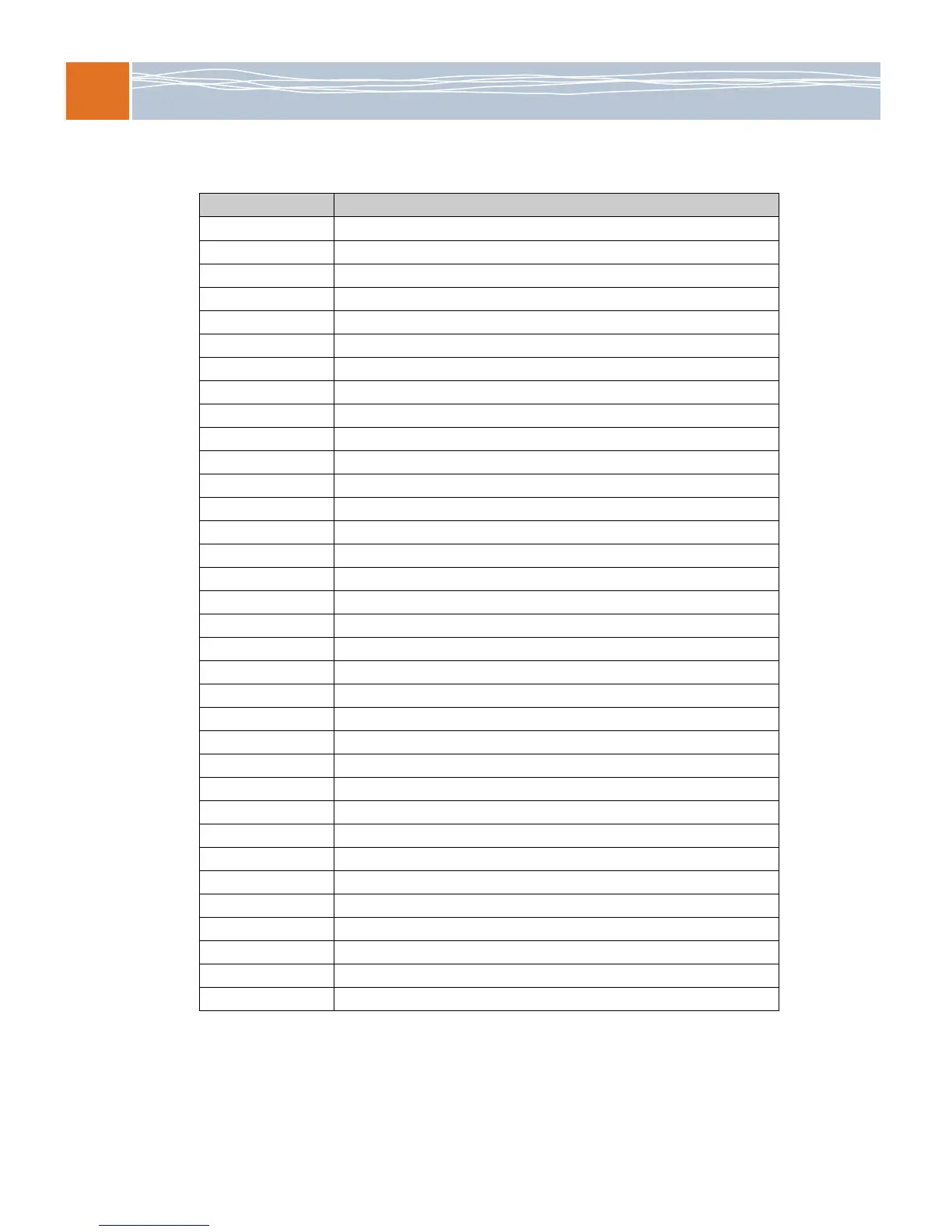

Intel memory initialization checkpoint codes

Checkpoint Code Description

A0h Detects GMCH device.

A1h Progress meter inside routine: DDRProgRCOMP

A2h Progress meter inside routine: DDRProgRCOMP

A3h Progress meter inside routine: DDRProgRCOMP

A4h Progress meter inside routine: DDRProgRCOMP

A5h Progress meter inside routine: DDRProgRCOMP

A6h Progress meter inside routine: DDRProgRCOMP

A8h Progress meter inside routine: DDRProgRCOMP

AAh Begin Common Initialization.

ABh ProgDRADRBs

ACh Init_Chipset_For_ECC

B0h Program DRAM timing register.

B1h Bad CAS latency.

C0h Executes JEDEC init.

C1h Executes JEDEC1 init.

D0h Programs the Chipset ECC functionality.

D1h Programs the CKE Tristate bits for unpopulated rows.

D2h Programs the FSB Slew Rate Lookup Table.

D3h Programs the DVO Slew Rate Lookup Table.

D5h Programs the MMAC register.

D6h Programs the MMAC register (completed)

E1h Not all memory sticks present are DDR.

E2h Not all memory sticks present are unbuffered.

E3h No DIMMS are detected.

E4h No DIMMs detected with good CAS latencies.

E5h Too many performance grades detected.

E6h Cannot find least common TRAS for all DIMMS present.

E7h Cannot find least common TRP for all DIMMS present.

E8h Cannot find least common TRCD for all DIMMS present.

E9h Cannot determine highest common refresh rate for all DIMMs present.

EAh A coding error has been detected.

EBh Not all memory sticks present have the same sided-ness.

ECh At least one DIMM stick present is in neither x8 nor x16 format.

EDh Invalid memory configuration (generic).

Loading...

Loading...