16 MHz provide additional

CAUTION!

20 MHz provide additional

(E0VCC)*1

(VSS)*1

(VSS)*1

(E0VCC)*1

5mOhm @ 500kHz

Each capacitor ESR

9mOhm @ 1MHz

crystal

24 MHz provide additional

Connect VSS per vias to SVRDRVSS

Fri Jan 7 07:49:03 2022

SG8018CE-20.000000MHz

DNF/DNB

3.3V or 5V

A0VREFH

3.3V or 5V

100n

SPM6545VT-100M-D

3.3V or 5V

A2VREFH

15u

100n

3.3V or 5V

VCC

3.3V or 5V

100n 100n 100 n

100n 100n 100n

100n100n100n100n 100n 100n

1.12V

VDD

100n 100n

100n 100n

3.3V or 5V

E2VCC

100n 100n

SVRAVCC

40.000 MHz + socket

16MHz

DNF/DNB

22p

SVRDRVCC

Testpoint_small_rd

47u

SYSVCC

3.3V or 5V 3.3V or 5V3.3V or 5V

1u

A1VREF H A2VREFH

3.3V or 5V

SVRAVCC

3.3V or 5V

SYSVCC

3.3V or 5V

VDD

1.12V

VCC

3.3V or 5V

E0VCC

3.3V or 5V

3.3V or 5V

E2VCC

A0VREFH

SVR_OUTPUT

1.09V

RTR040N03HZGTL

100n100n 100n

E0VCC

3.3V or 5V

E1VCC

100n

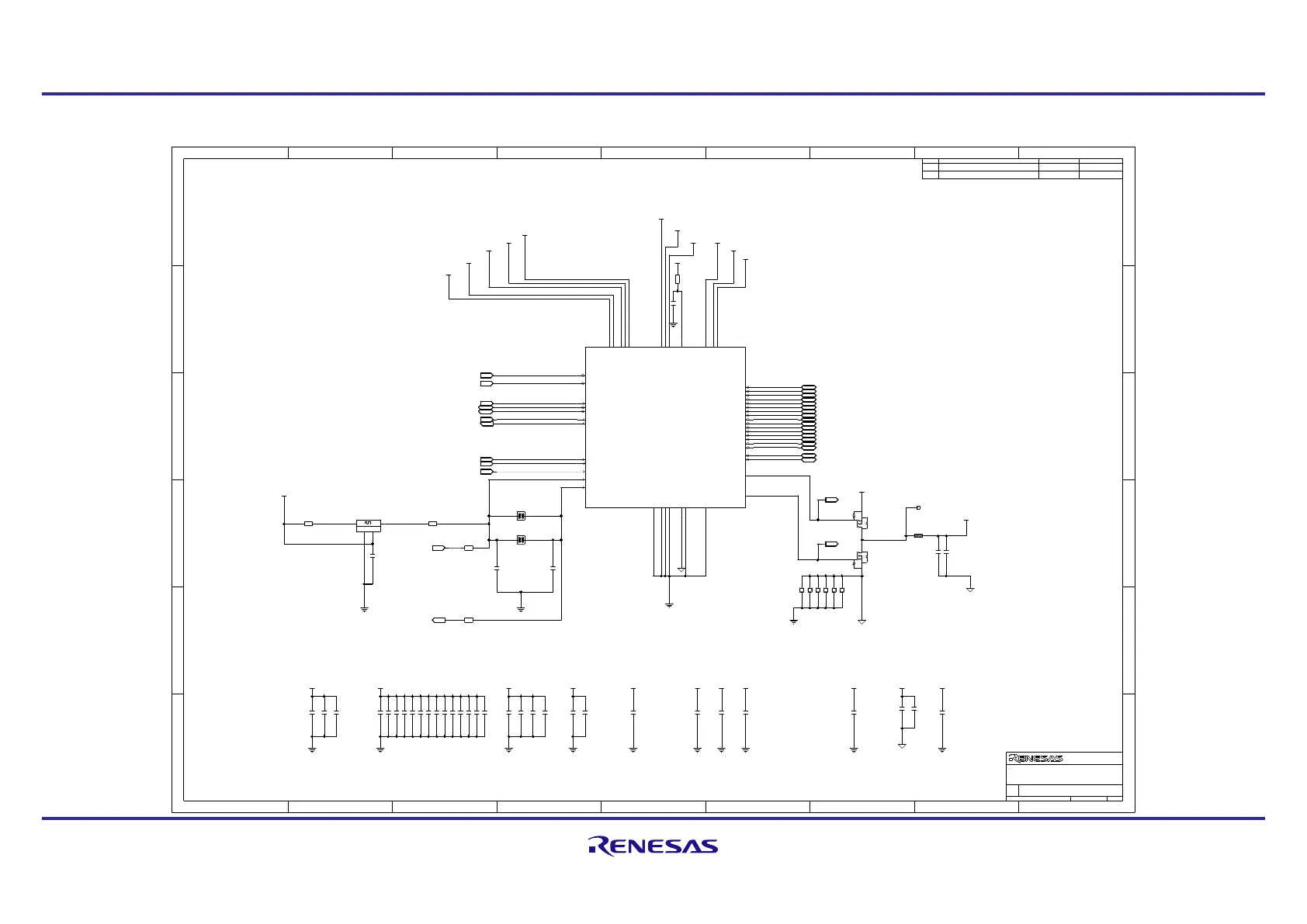

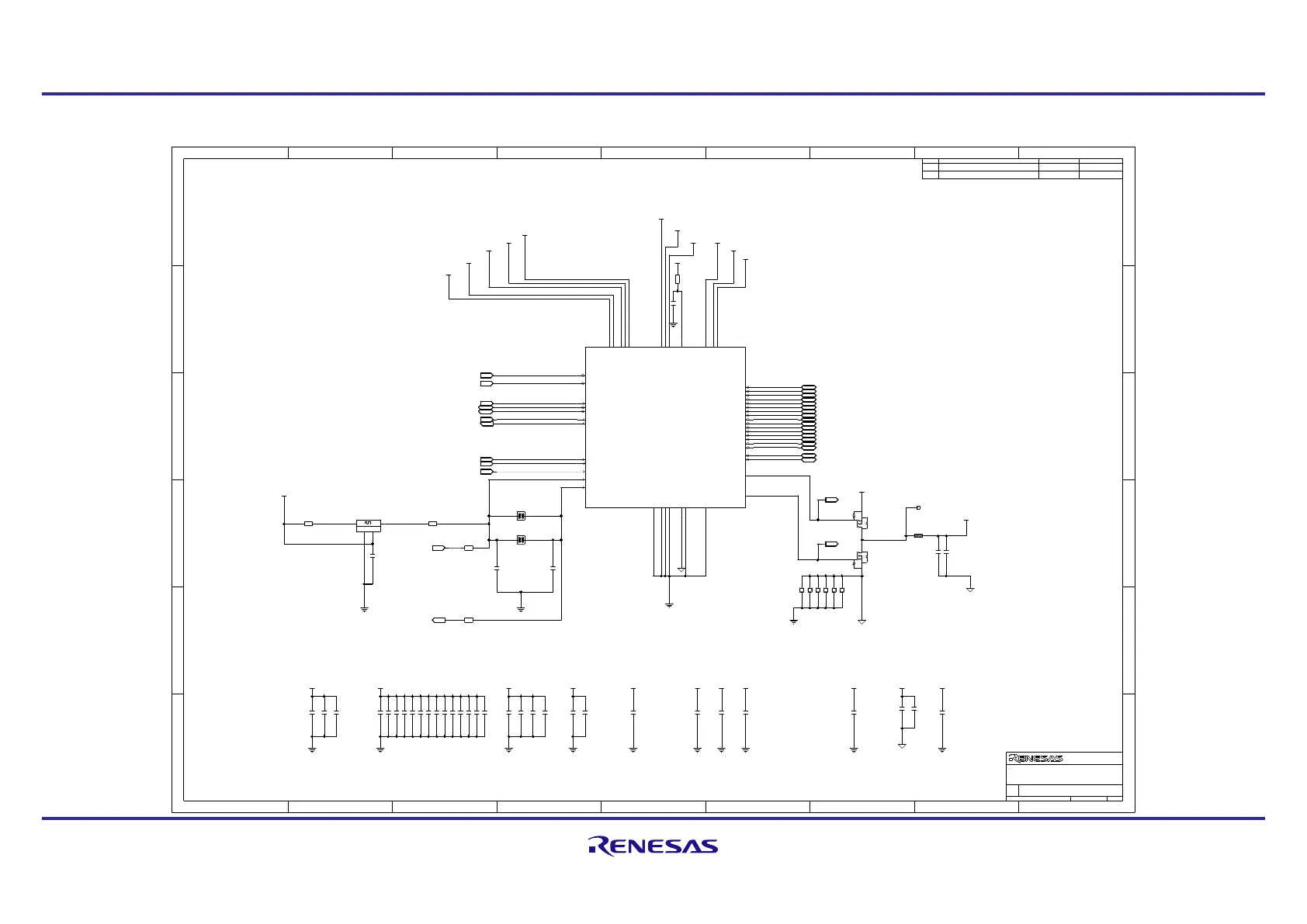

u2a_144_enplas

3.3V or 5V

DNF/DNB

3.3V or 5V

E1VCC

A1VREFH

1K0

DNF/DNB

P3V3

3.3V

8pF

3.3V or 5V

100n

0

DNF/DNB

0

0

DNF/DNB

220n

DNF/DNB

22p

18pF

10uH

47u

100n 100n

3.3V or 5V

3.3V or 5V

AWOVCL

100

220n

100n 100n

Electronics Europe GmbH

rh850_u2a_144pin_pb_t1_v1

D018888_04

1.00

20220106 L.Stark

PAGE 1 OF 5

SVRDRVCC

SVRDRVCC

RTR030P02HZGTL

R1

C16

OSC1

R4

R2

R3

X1

TR1

L1

TR2

C19

C36C1 C3 C

4 C6 C7 C9

C10 C37 C43 C56 C62 C63 C64C3

8 C39 C45

C12

TP10

C13

C5

C97

C98

X3

C68 C69C20 C22 C2 3

C25

C24

R58

FS1

FS2

FS3

FS4

FS5

FS6

IC1

C

2 C8 C41 C4

4 C73 C14

4A1

2A8

2B8

5B9

5B3

2B3 5B3

4A5

5A3 5A4 5B1 5B3 5B6

2B2 2B3 5B4

5B6

2B2 2B3

2D2 2D3 5A4

5A6 5B1 5B4

5B6 5 C7

5C9

2A22A32B22B35C15C35 C75C9

5B75B9

5C1

5C35C7

5C9

2B3 5 C1

5C92D2

2D8

2C6 2D3 4C5

5B3 5B6 5B9

2D2

2D33E54A1

2B2 2B3 5B9

5C1 5C7 5C9

2C6

5B9

2D6 2D8

5A7 5A9

2C6

5B3 5B4

2C2 2C3

2D2 5B1 5B3

5B7

2A6 2B6

2B8 5A6 5A7 5B1 5B7 5B9

5C1 5C3 5C7 5C9

2B6 2B8 5B7

2D2

2D84C1

2D24C7

2C8

5B9

2D34A1

2D3

2A6 2 D6 2D8

5B3 5 C3

2D6 2D8

5B1 5B3 5C1

5C3

2D22D3

4A1

2D2

5B4

5A7

2B32B2

2D6

SVRDRVSS

RESETZ

P24<8..7>

P4<0>

P4<10..5>

P4<15..13>

P3<7..2>

AP0<9..0>

AP2<9..0>

P24<11>TRSTZ

DCDC_P

X1

P5<4..2>

X2_C

P2<0>

P2<15..11>

P5<6>

P6<6..4>

P6<15..8>

P10<14..0>

P17<1..0>

VMONOUT Z

DCDC_N

ERROROUTZ

FLMD0

P2<2>

P17<5>

JP0<5>

PWRCTL

X2

P20<14..12>

P20<10..1>

JP0<3..0>

X1_C

3

2

1

4

3

1

23

1

2

1

37

38

3536

74

73

103

56

144

97

90

113

112

52

111

18

60

104

96

114

115

119

116

117

118

102

95

105

101

99

EPAD[3..0]

VMONOUT

SYSVCC

SVRPGATE

SVRNGATE

SVRDRVSS

SVRDRVCC

SVRAVSS

SVRAVCC

ERROROUT_M

E2VCC

AWOVCL

A2VSS

A2VREFH

A1VSS

A1VREFH

A0VSS

A0VREFH

FLMD0

P5[6]

P4[0]

P2[2]

P2[0]

P24[11]

P17[5]

JP0[5]

PWRCTL

RESET

TRST

X1

X2

E0VCC[3..0]

E1VCC[1..0]

VCC[1..0]

VDD[13..0]

VSS[1..0]

AP2[9..0]

AP0[9..0]

P6[6..4]

P6[15..8]

P5[4..2]

P4[15..13]

P4[10..5]

P3[7..2]

P2[15..11]

P24[8..7]

P20[14..12]

P20[10..1]

P17[1..0]

P10[14..0]

JP0[3..0]

BI

BI

OE

VCCGND

CLK

IN

OUT

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

IN

S

D

G

D

S

G

IN

IN

IN

IN

IN

IN

OUT

BI

BI

BI

BI

BI

BI

OUT

OUT

DATE DRAWN BY

REV

COMMENT

WS Release

1.0

Size Document Number

A2

Title

Date:

987654321

9

87

6

5

4321

A

B

C

D

E

F

A

B

C

D

E

F

2B3 2D2

2D3 4C8 4C9

5B1 5B3 5B4 5B7

Loading...

Loading...