RL78/G13 CHAPTER 12 SERIAL ARRAY UNIT

R01UH0146EJ0100 Rev.1.00 549

Sep 22, 2011

(3) Serial mode register mn (SMRmn)

The SMRmn register is a register that sets an operation mode of channel n. It is also used to select an operation

clock (f

MCK), specify whether the serial clock (fSCK) may be input or not, set a start trigger, an operation mode (CSI,

UART, or simplified I

2

C), and an interrupt source. This register is also used to invert the level of the receive data

only in the UART mode.

Rewriting the SMRmn register is prohibited when the register is in operation (when SEmn = 1). However, the

MDmn0 bit can be rewritten during operation.

The SMRmn register can be set by a 16-bit memory manipulation instruction.

Reset signal generation sets the SMRmn register to 0020H.

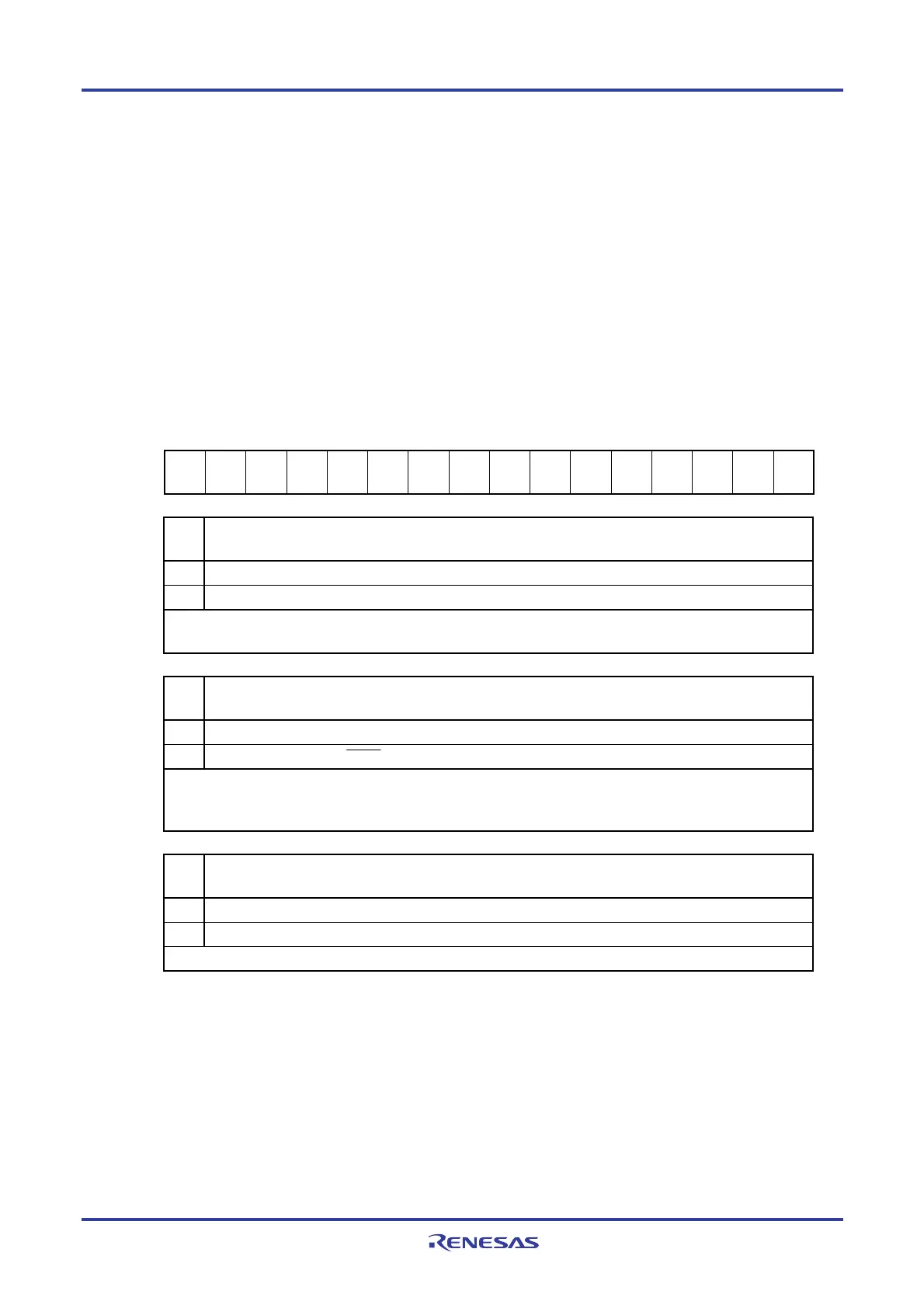

Figure 12-7. Format of Serial Mode Register mn (SMRmn) (1/2)

Address: F0110H, F0111H (SMR00) to F0116H, F0117H (SMR03), After reset: 0020H R/W

F0150H, F0151H (SMR10) to F0156H, F0157H (SMR13)

Symbol 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SMRmn

CKS

mn

CCS

mn

0 0 0 0 0

STS

mn

Note

0

SIS

mn0

Note

1 0 0

MD

mn2

MD

mn1

MD

mn0

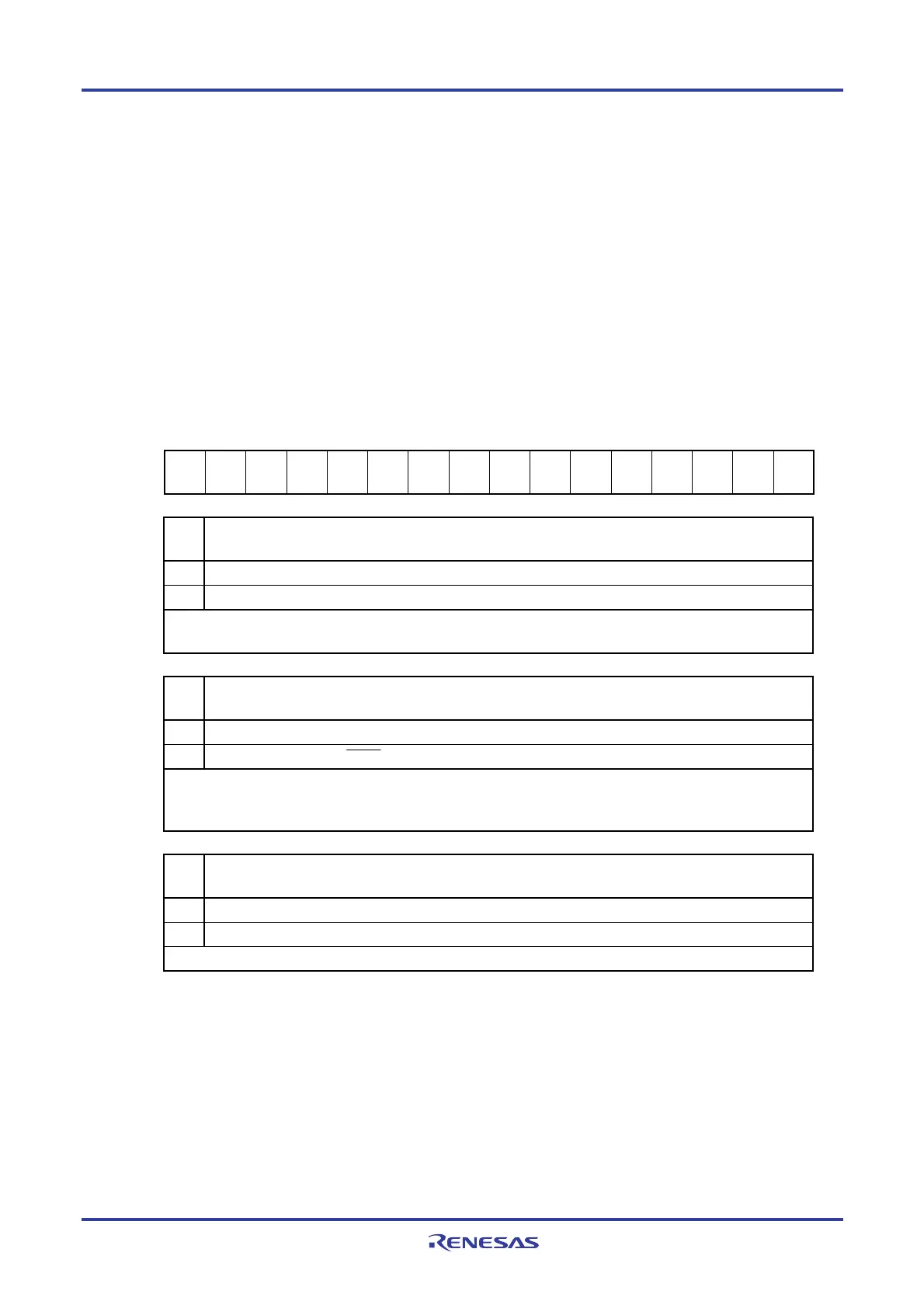

CKS

mn

Selection of operation clock (f

MCK) of channel n

0 Operation clock CKm0 set by the SPSm register

1 Operation clock CKm1 set by the SPSm register

Operation clock (fMCK) is used by the edge detector. In addition, depending on the setting of the CCSmn bit and the

higher 7 bits of the SDRmn register, a transfer clock (f

TCLK) is generated.

CCS

mn

Selection of transfer clock (f

TCLK) of channel n

0 Divided operation clock fMCK specified by the CKSmn bit

1 Clock input fSCK from the SCKp pin (slave transfer in CSI mode)

Transfer clock fTCLK is used for the shift register, communication controller, output controller, interrupt controller, and

error controller. When CCSmn = 0, the division ratio of operation clock (f

MCK) is set by the higher 7 bits of the

SDRmn register.

STS

mn

Selection of start trigger source

0 Only software trigger is valid (selected for CSI, UART transmission, and simplified I

2

C).

1 Valid edge of the RXDq pin (selected for UART reception)

Transfer is started when the above source is satisfied after 1 is set to the SSm register.

Note The SMR01, SMR03, SMR11, and SMR13 registers only.

Caution Be sure to clear bits 13 to 9, 7, 4, and 3 (or bits 13 to 6, 4, and 3 for the SMR00, SMR02, SMR10, or

SMR12 register) to “0”. Be sure to set bit 5 to “1”.

Remark m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3), p: CSI number (p = 00, 01, 10, 11, 20, 21, 30,

31), q: UART number (q = 0 to 3), r: IIC number (r = 00, 01, 10, 11, 20, 21, 30, 31)

Loading...

Loading...