RL78/G13 CHAPTER 19 RESET FUNCTION

R01UH0146EJ0100 Rev.1.00 874

Sep 22, 2011

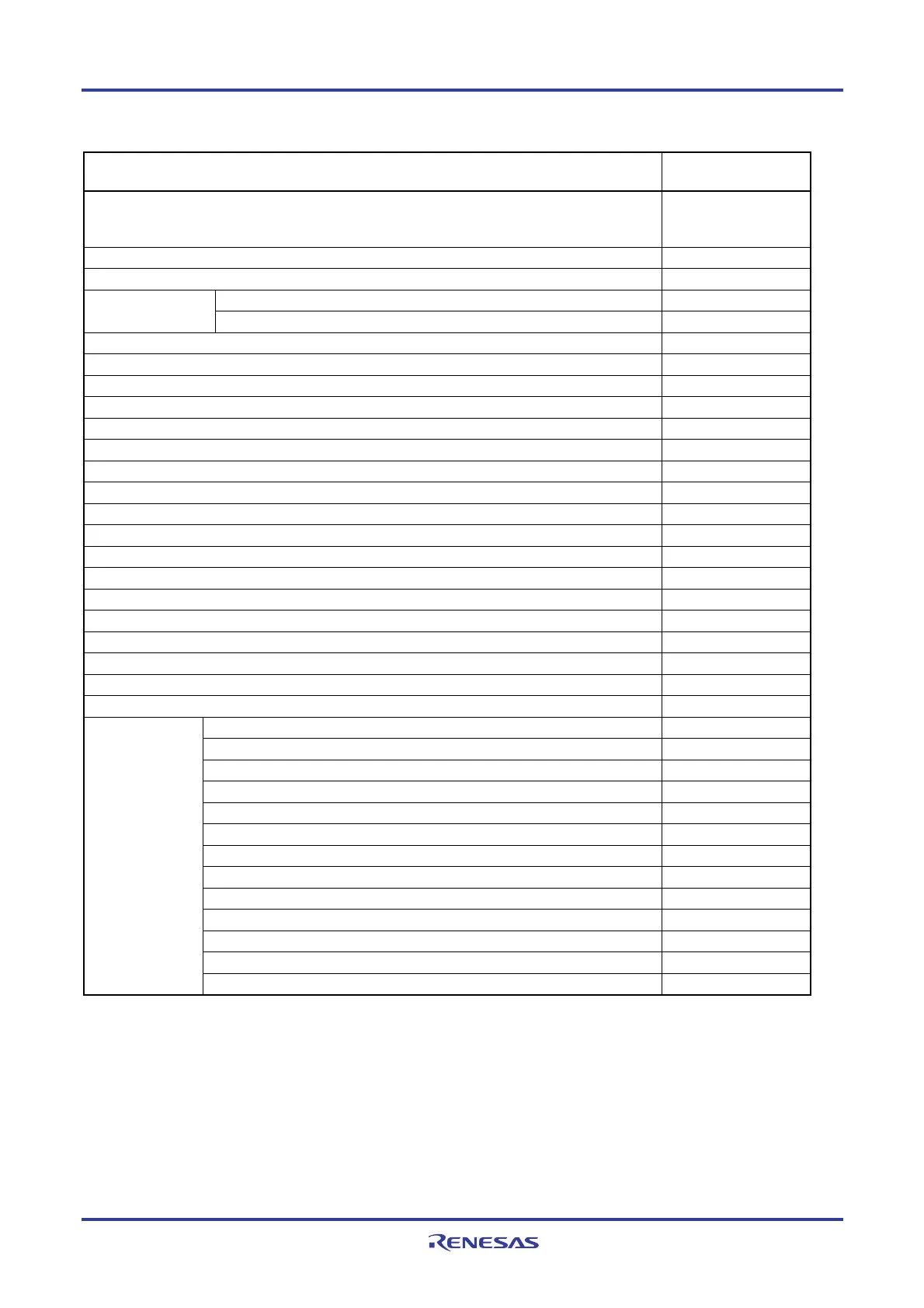

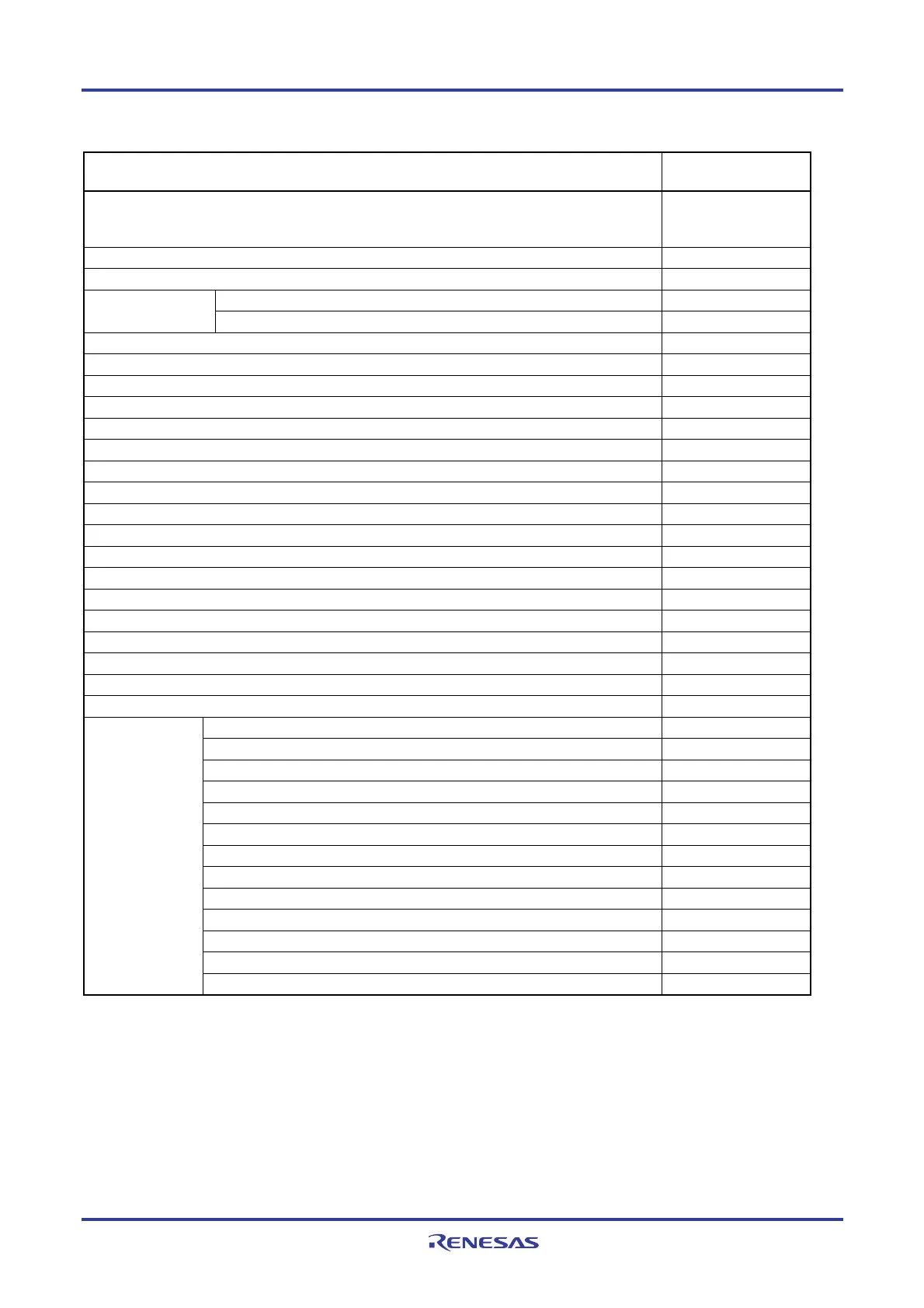

Table 19-2. Hardware Statuses After Reset Acknowledgment (1/4)

Hardware After Reset

Acknowledgment

Note 1

Program counter (PC) The contents of the

reset vector table

(0000H, 0001H) are set.

Stack pointer (SP) Undefined

Program status word (PSW) 06H

Data memory Undefined RAM

General-purpose registers Undefined

Processor mode control register (PMC) 00H

Port registers (P0 to P15) (output latches) 00H

Port mode registers (PM0 to PM12, PM14, PM15) FFH

Port mode control registers (PMC0 to PMC3, PMC10, PMC11, PMC12, PMC14) FFH

Port input mode registers (PIM0, PIM1, PIM4, PIM5, PIM8, PIM14) 00H

Port output mode registers (POM0, POM1, POM4, POM5, POM7 to POM9, POM14) 00H

Pull-up resistor option registers (PU0, PU1, PU3 to PU12, PU14) 00H (PU4 is 01H)

Peripheral I/O redirection register (PIOR) 00H

Clock operation mode control register (CMC) 00H

Clock operation status control register (CSC) C0H

System clock control register (CKC) 00H

Oscillation stabilization time counter status register (OSTC) 00H

Oscillation stabilization time select register (OSTS) 07H

Noise filter enable registers 0, 1, 2 (NFEN0, NFEN1, NFEN2) 00H

Peripheral enable register 0 (PER0) 00H

High-speed on-chip oscillator frequency select register (HOCODIV) Undefined

High-speed on-chip oscillator trimming register (HIOTRM) Note 2

Operation speed mode control register (OSMC) 00H

Timer data registers 00 to 07, 10 to 17 (TDR00 to TDR07, TDR10 to TDR17) 0000H

Timer mode registers 00 to 07, 10 to 17 (TMR00 to TMR07, TMR10 to TMR17) 0000H

Timer status registers 00 to 07, 10 to 17 (TSR00 to TSR07, TSR10 to TSR17) 0000H

Timer input select register 0, 1 (TIS0, TIS1) 00H

Timer counter registers 00 to 07, 10 to 17 (TCR00 to TCR07, TCR10 to TCR17) FFFFH

Timer channel enable status register 0, 1 (TE0, TE1) 0000H

Timer channel start register 0, 1 (TS0, TS1) 0000H

Timer channel stop register 0, 1 (TT0, TT1) 0000H

Timer clock select register 0, 1 (TPS0, TPS1) 0000H

Timer output register 0, 1 (TO0, TO1) 0000H

Timer output enable register 0, 1 (TOE0, TOE1) 0000H

Timer output level register 0, 1 (TOL0, TOL1) 0000H

Timer array unit

Timer output mode registers 0, 1 (TOM0, TOM1) 0000H

Notes 1. During reset signal generation or oscillation stabilization time wait, only the PC contents among the hardware

statuses become undefined. All other hardware statuses remain unchanged after reset.

2. The reset value differs for each chip.

Remark The special function register (SFR) mounted depend on the product. See 3.1.4 Special function registers

(SFRs) and 3.1.5 Extended special function registers (2nd SFRs: 2nd Special Function Registers).

<R>

<R>

Loading...

Loading...