RL78/G13 CHAPTER 19 RESET FUNCTION

R01UH0146EJ0100 Rev.1.00 878

Sep 22, 2011

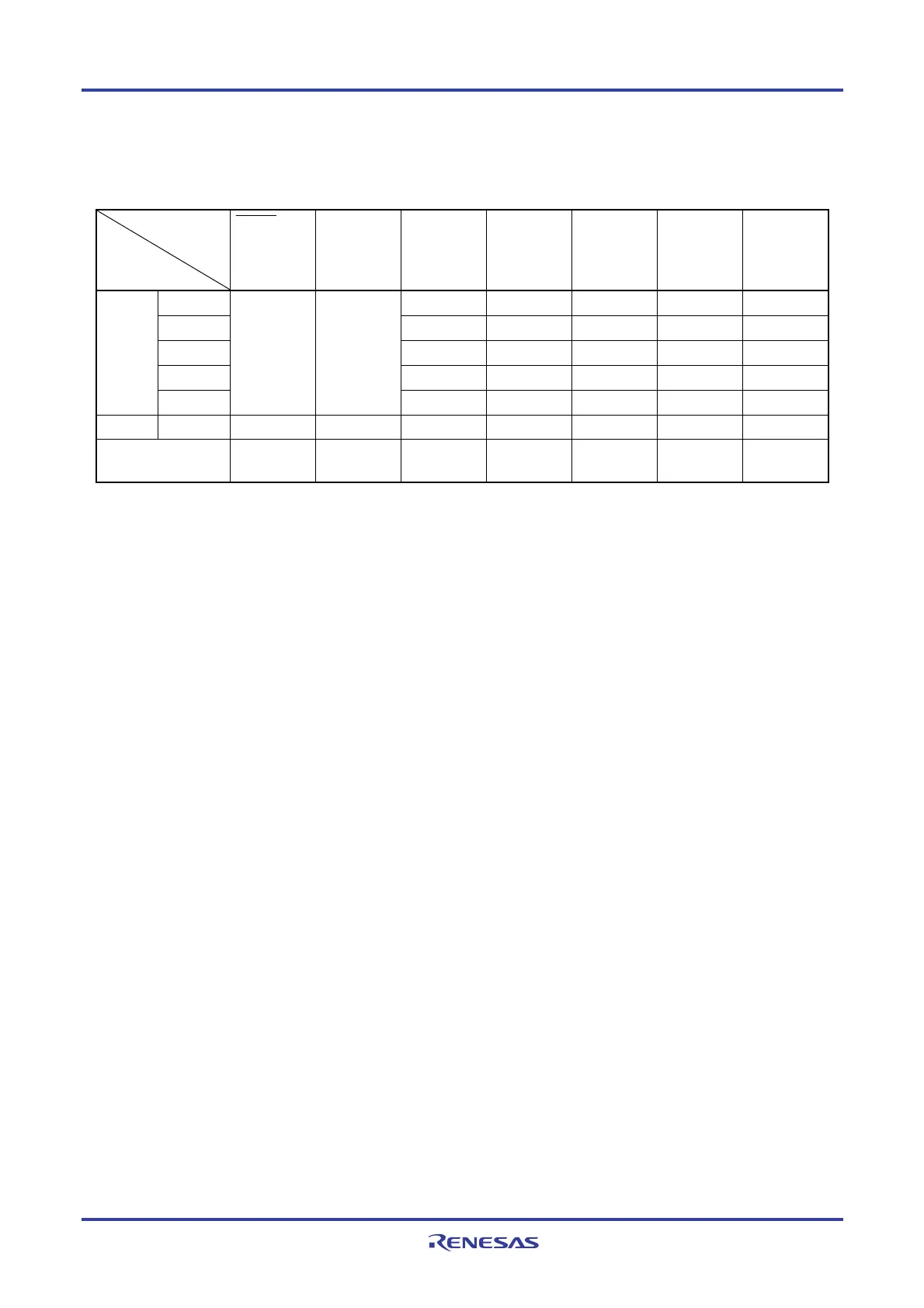

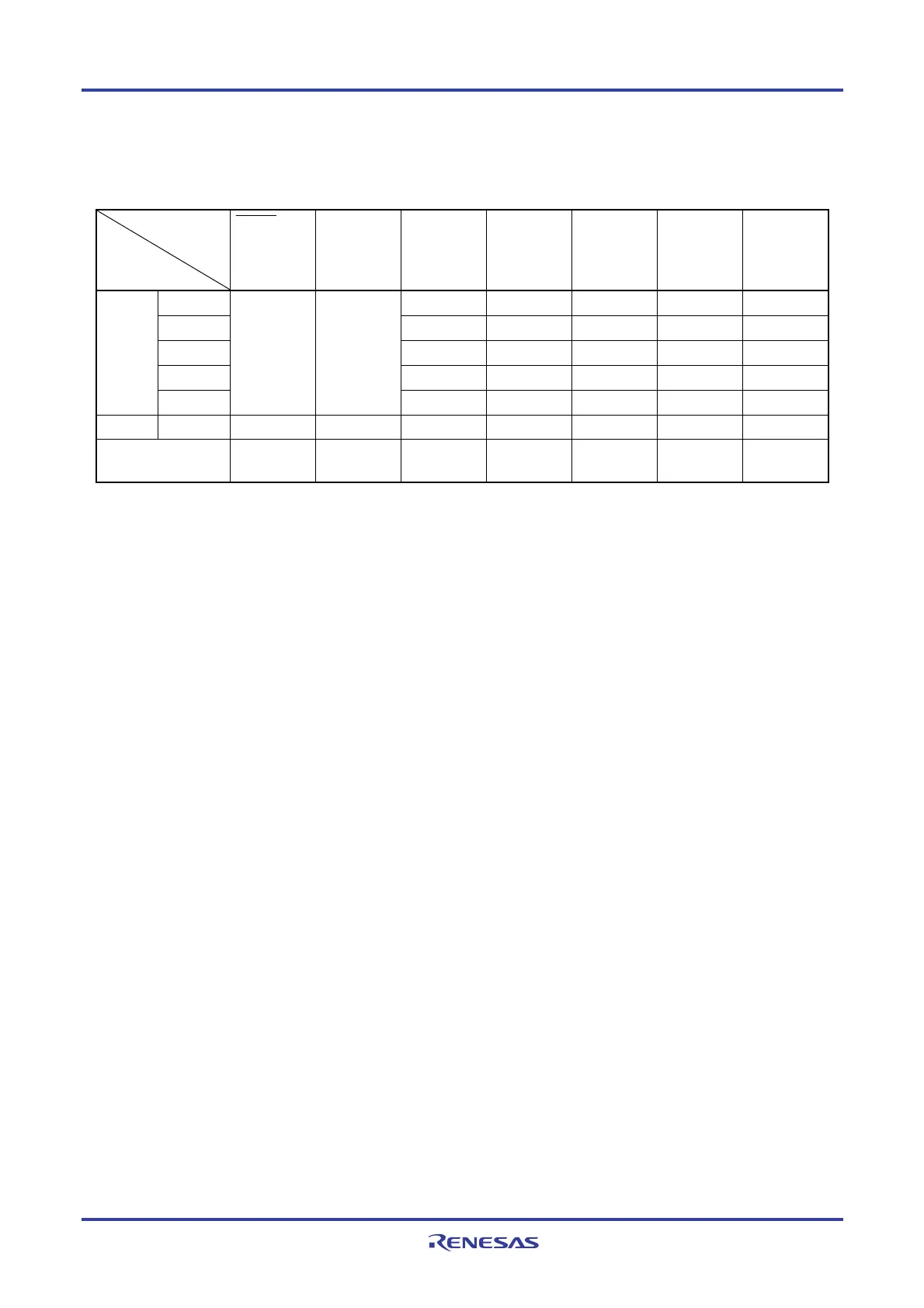

Notes 1. During reset signal generation or oscillation stabilization time wait, only the PC contents among the hardware

statuses become undefined. All other hardware statuses remain unchanged after reset.

2. These values vary depending on the reset source.

Reset Source

Register

RESET Input

Reset by

POR

Reset by

Execution of

Illegal

Instruction

Reset by

WDT

Reset by

RAM parity

error

Reset by

illegal-

memory

access

Reset by

LVD

TRAP bit Set (1) Held Held Held Held

WDTRF bit Held Set (1) Held Held Held

RPERF bit Held Held Set (1) Held Held

IAWRF bit Held Held Held Set (1) Held

RESF

LVIRF bit

Cleared (0) Cleared (0)

Held Held Held Held Set (1)

LVIM LVISEN Cleared (0) Cleared (0) Cleared (0) Cleared (0) Cleared (0) Cleared (0) Held

LVIS

Cleared

(00H/01H/81H)

Cleared

(00H/01H/81H)

Cleared

(00H/01H/81H)

Cleared

(00H/01H/81H)

Cleared

(00H/01H/81H)

Cleared

(00H/01H/81H)

Held

3. The generation of reset signal other than an LVD reset sets as follows.

• When option byte LVIMDS1, LVIMDS0 = 1, 0: 00H

• When option byte LVIMDS1, LVIMDS0 = 1, 1: 81H

• When option byte LVIMDS1, LVIMDS0 = 0, 1: 01H

Remark The special function register (SFR) mounted depend on the product. See 3.1.4 Special function registers

(SFRs) and 3.1.5 Extended special function registers (2nd SFRs: 2nd Special Function Registers).

<R>

<R>

Loading...

Loading...