Technical Data P746/EN TD/G31

MiCOM P746

(TD) 2-7

TD

IEC 61850 Ethernet data

10 Base T /100 Base TX Communications

Interface in accordance with IEEE802.3 and

IEC61850

Isolation 1.5kV

Cable type: Screened twisted pair STP

Max length: 100m

100 Base FX Interface

Interface in accordance with IEEE802.3 and

IEC61850

Wavelength: 1300nm

Fibre: multi-mode 50/125µm or 62.5/125µm

Connector style: ST

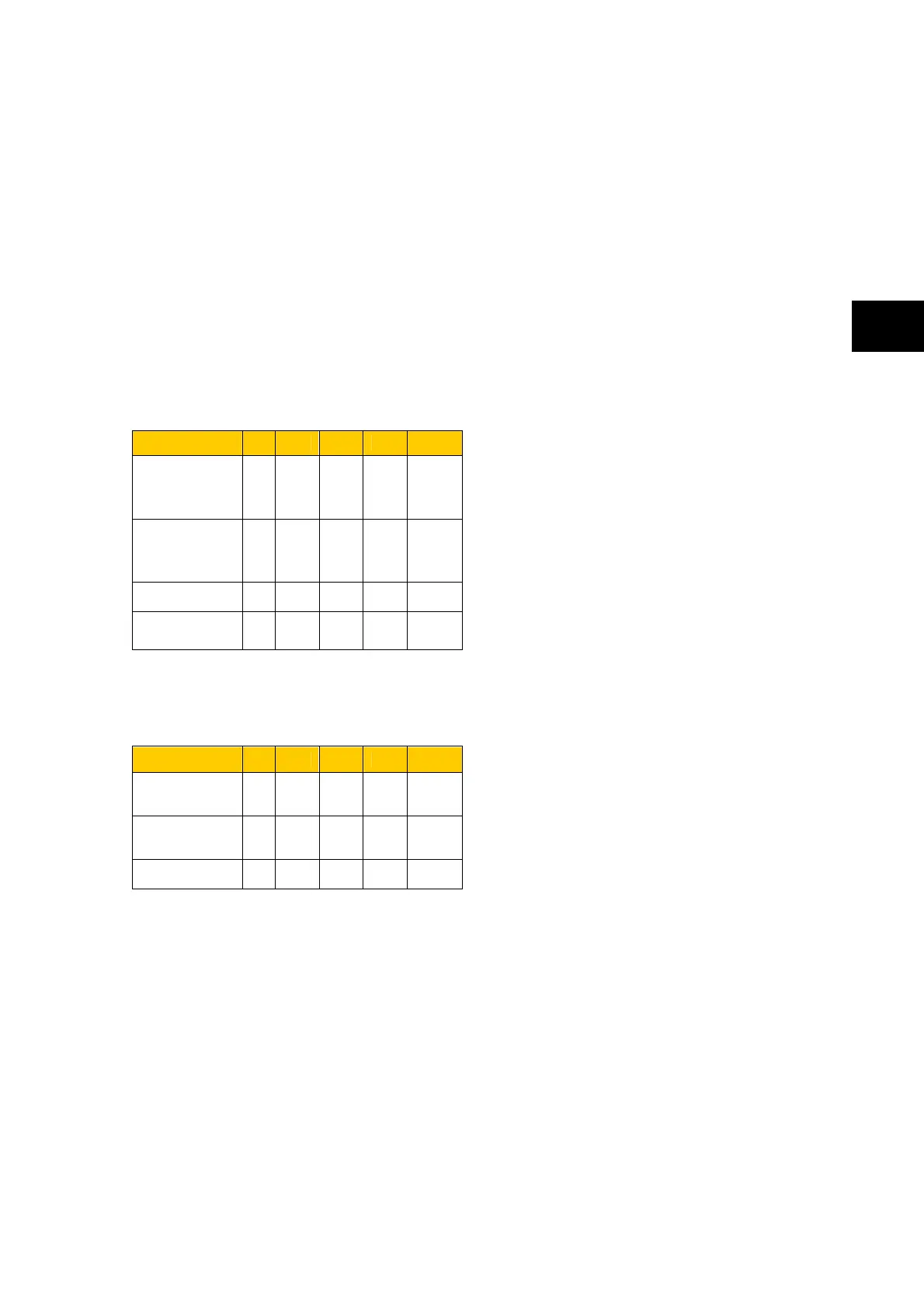

Transmitter Optical Characteristics

(TA = 0°C to 70°C, VCC = 4.75 V to 5.25 V)

Parameter Sym Min. Typ. Max Unit

Output Optical

Power

BOL 62.5/125 µm,

NA = 0.275 Fiber

EOL

PO

-19

-20

-16.8 -14

dBm avg.

Output Optical

Power

BOL 50/125 µm,

NA = 0.20 Fiber

EOL

PO

-22.5

-23.5

-20.3 -14

dBm avg.

Optical Extinction

Ratio

10

-10

%

dB

Output Optical

Power at

Logic “0” State

PO

(“0”)

-45

dBm avg.

BOL – Beginning of life

EOL – End of life

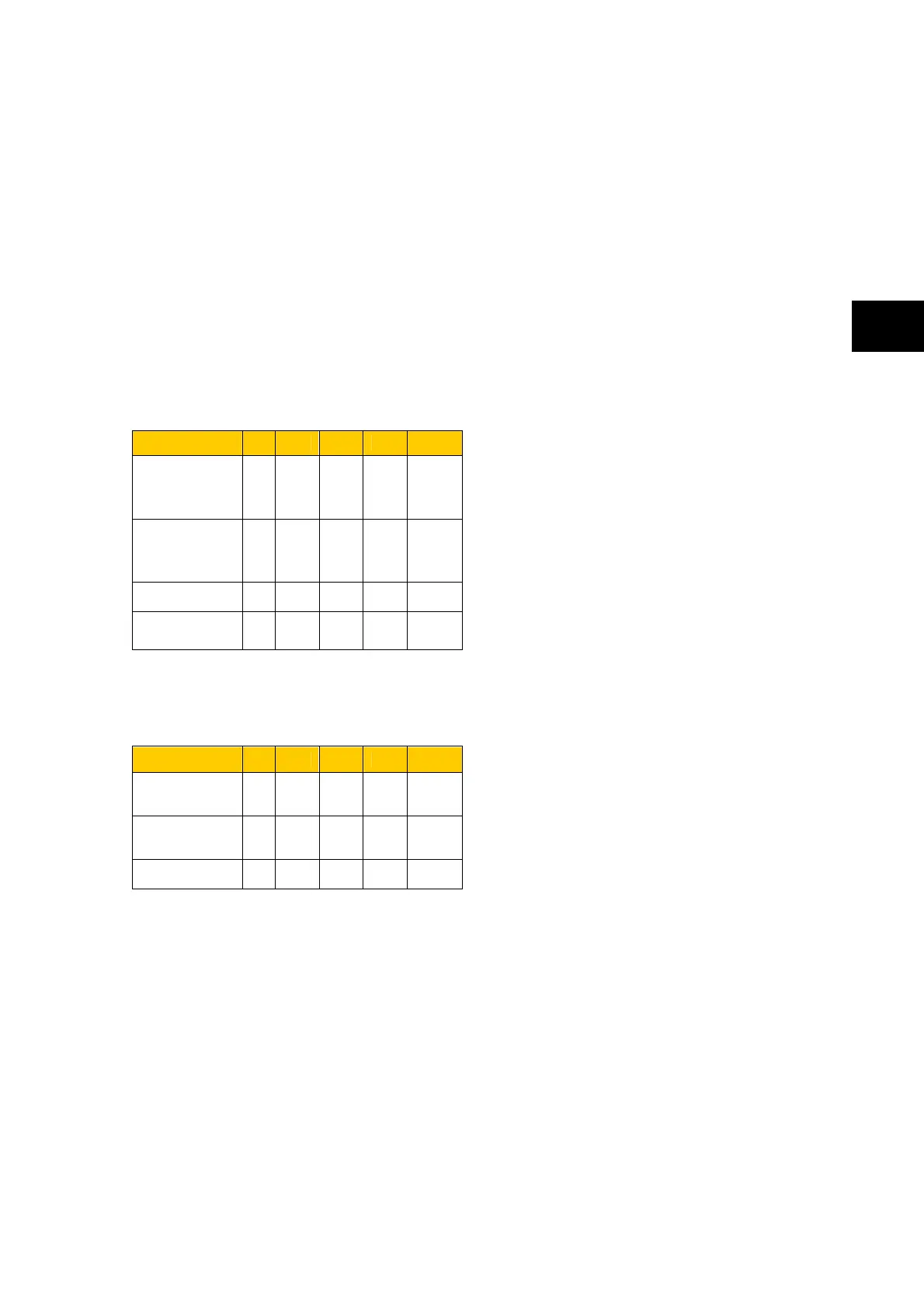

Receive Optical Characteristics

(TA = 0°C to 70°C, VCC = 4.75 V to 5.25 V)

Parameter Sym Min. Typ. Max. Unit

Input Optical

Power Minimum at

Window Edge

PIN

Min.

(W)

-33.5 –31 dBm avg.

Input Optical

Power Minimum at

Eye Center

PIN

Min.

(C)

-34.5 -31.8 Bm avg.

Input Optical

Power Maximum

PIN

Max.

-14 -11.8 dBm avg.

Settings, Measurements and

Records List

Global Settings (System Data):

Language:

∗ English/French/German/Spanish

Frequency:

∗ 50/60Hz

Voltage transformers

Phase VT Primary: 100V...100kV

Phase VT Secondary V: 80…140V

Current transformers

Phase CT Primary: 1A...30kA

Phase CT Secondary I

n

: 1A or 5A

Current transformer and feeder

characteristics

Class:

∗ 5P (IEC185)

∗ X (BS3958)

∗ TPX (IEC 44-6)

∗ TPY (IEC 44-6)

∗ TPZ (IEC 44-6)

Supervision of I

0

calculation:

∗ Kce: 0.01... 1.00

I

0

error alarm time delay:

∗ Tce: 0.0...10.0 s

Differential Protection

IRef:

∗ 100A…30kA (step 5A)

Disabled/Enabled

I

D

>2:

∗ 10%…250% (step 1%)

k2:

∗ 20%...90% (step 1%)

tDiff:

∗ 0…10s (step 10ms)

Check zone

kCZ:

∗ 0%…90% (step 1%)

Circuitry fail

Disabled/Enabled

I

D

>1:

∗ 5%…600% (step 1%)

k1:

∗ 0%…50% (step 1%)

tI

D

>1:

∗ 0…600.0s (step 10ms)

CZ circuitry modes

Alarm & No Block / AlarmSR&No Block /

Blocking Latched / Alarm Latched / Sel-Reset

Zx circuitry modes

Self-Reset / Alarm Latched / Blocking Latched

Circuitry fail blocking mode:

∗ per phase/3 phase

Circuitry reset:

∗ 0…600.0s (step 100ms)

Loading...

Loading...