2008-03-14

LC-32A28L, LC-42A48L

51

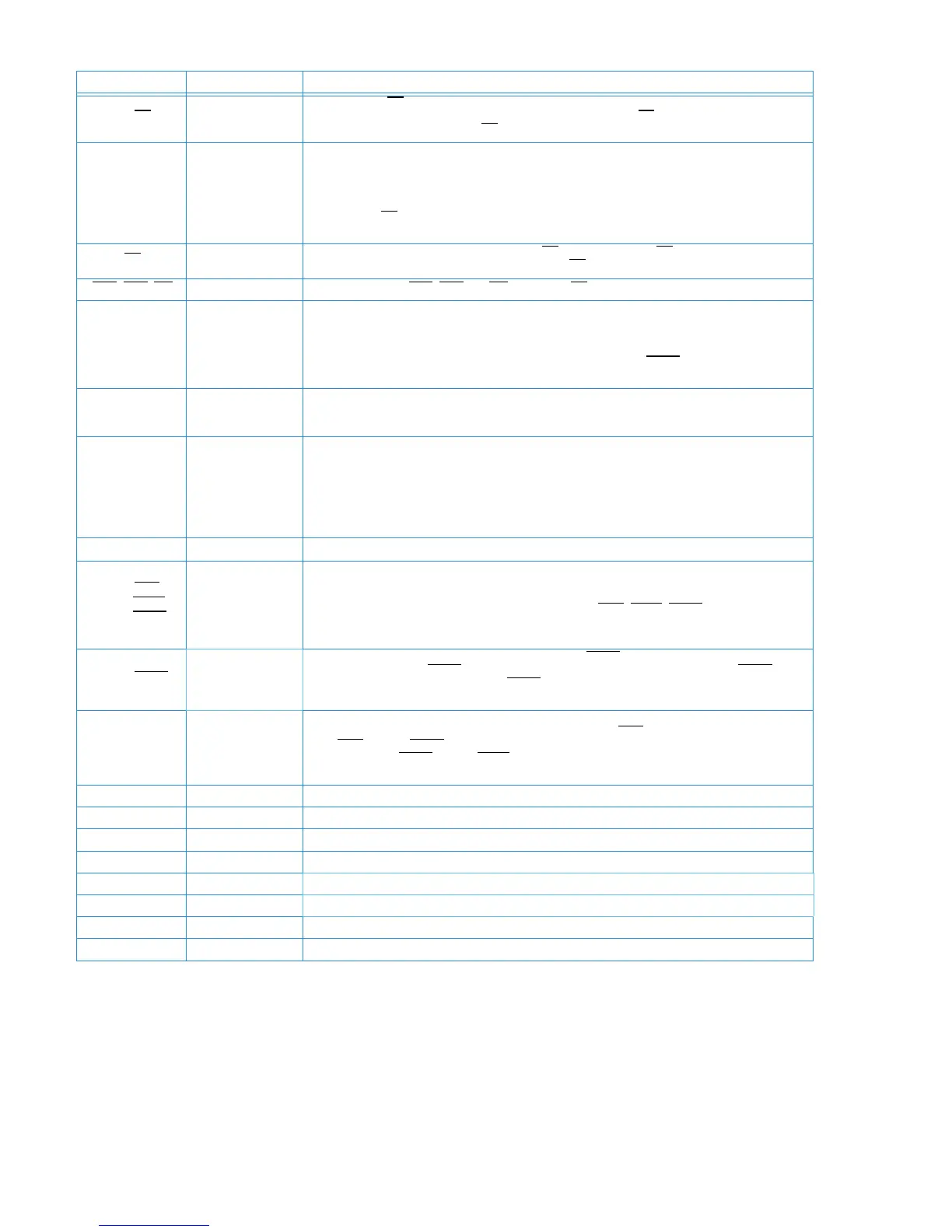

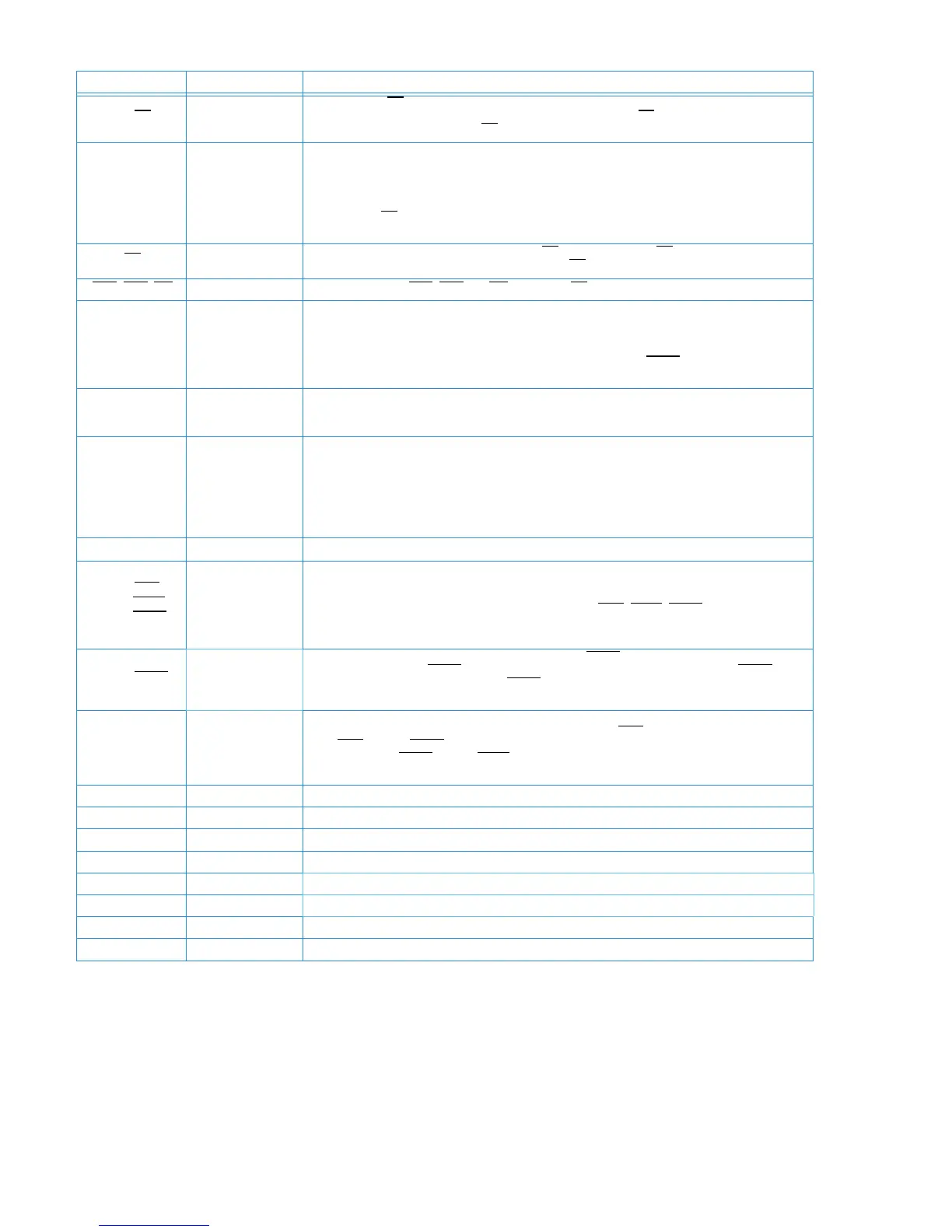

Input/Output Functional Description

Symbol Type Function

CK, CK

Input

Clock: CK and CK are differential clock inputs. A ll addres s and control input signals are sampled

on t h e crossing of the positive edge of CK and negative edge of CK. Output (read) data is refer-

enced to the crossings of CK and CK (both directions of crossing).

CKE Input

Clock Enable: CKE high activates and CKE low deactivates internal clock signals and device

input buffers and output drivers. Taking CKE low provides Precharge Power-Down and Self-

Refresh operation (all banks idle), or Active Power-Down (row Active in any bank). CKE is syn-

chronous for power down entry and exit and for Self-Refresh entry. CKE is asynchronous for Self-

Refresh exit. CKE must be maintained high throughout read and write accesses. Input buf f ers,

excluding CK, CK, ODT and CKE are disabled during Power Down. I nput buffers, excluding C KE

are disabled during Self-Refresh.

CS Input

Chip Select: All command ar e masked when CS is registered high. CS provides for external rank

selection on systems with multiple memory ranks. CS is cons id ered par t of the com mand code.

RAS, CAS, WE Input Command Inputs: RAS, CAS and WE (along with CS) define the com mand being entered.

DM, LDM, UDM Input

Input Data Mask: DM is an input mask signal for write data. Input data is masked when DM is

sampled high coincident with that input data during a Write access. DM is sampled on both edges

of DQS. Although DM pins are input only, the DM loading matches the DQ and DQS loading. LDM

and UDM are the input mask signals for x16 components and control the lower or upper byte s. For

x8 components the data mask function is disabled, when RDQ S / RQDS are ena bled by EMR(1)

command.

BA0, BA1 Input

Bank Address Inputs: BA0 and BA1 define to which bank an Active, Read, Write or Precharge

command is being applied. BA0 and BA 1 also det ermines if the m ode register or extended m o de

register is to be accessed during a MRS or EMR cycle.

A0 - A13 Input

Address Inputs: Provides the row address for Activate commands and the column address and

Auto-Precharge bit A10 (=AP) f or Read/ Write commands to select one location out of the memory

array in the respective bank. A 10 (=A P) is sampled during a Precharge command to determine

whether the Precharge applies to one bank (A10=low) or all banks (A10=high). If only o ne bank is

to be precharged, the bank is selected by BA0 and BA1. The address inputs also provide the op-

code during Mode Register Set commands.

Row address A13 is u sed on x 4 and x8 components only.

DQ

Input/Output Data Inputs/Output: Bi-directional data bus.

DQS, (DQS )

LDQS, (LDQS),

UDQS,(UDQS)

Input/Output

Data Strobe: output with read data, input with write data. Edg e aligned with read data, centered

with write data. For the x16, LDQS corresponds to the data on LDQ 0 - LDQ7; UDQS corresponds

to the data on U DQ 0-UDQ 7. The data strobes DQS, LDQS , UDQS may be used in single ended

mode or paired with the optional complementary signals DQS, LDQS, UDQS to provide differen-

tial pair signaling to the s ystem during both reads and writes. An EMR(1) control bit enables or dis-

ables t he complementary d ata strobe signals.

RDQS, (RDQS) Input/Output

Read Data Strobe: For the x8 components a RDQS, RDQS pair can be enabled via t he EMR(1)

for read timing. RDQS, RDQS is not supported on x4 and x16 components. RDQ S, RDQS are

edge-aligned wit h r ead data. If RDQ S, RDQS is enabled, the DM f unct ion is disabled on x8 com -

ponents.

ODT Input

On Die Termination: ODT (registered HIGH) enables termination resistance internal to the DDR2

SDRAM. When enabled, ODT is applied to each DQ , DQS, DQS and DM signal for x4 and DQ,

DQS, DQS , R DQS, RDQS and DM for x8 configurations. For x16 configuration ODT is applied to

each DQ, UDQS, UDQS, LDQS, LDQS , UDM and LDM signal. The ODT pin will be ignored if the

EMR(1) is programm ed to disable ODT.

NC No Connect: No internal elect rical connect ion is present .

V

DDQ

Supply DQ Power Supply: 1.8V +/- 0.1V

V

SSQ

Supply DQ Ground

V

DDL

Supply DLL Power Supply: 1.8V +/- 0.1V

V

SSDL

Supply DLL Ground

V

DD

Supply Power Supply: 1.8V +/- 0.1V

V

SS

Supply Ground

V

REF

Supply SSTL_1.8 reference voltage

Loading...

Loading...