A-7

Connecting TM I/O to PCS 7

C79000-G8076-C710-04

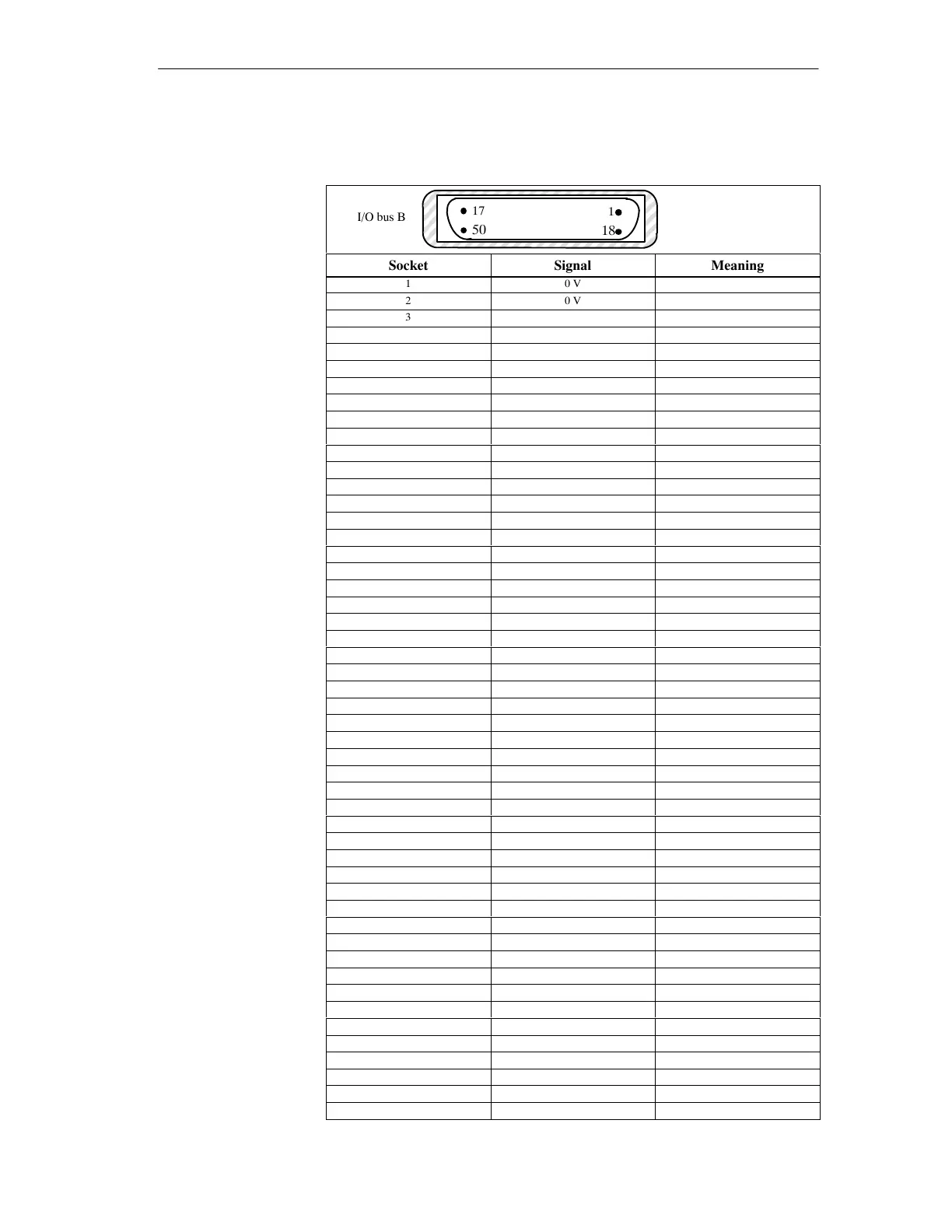

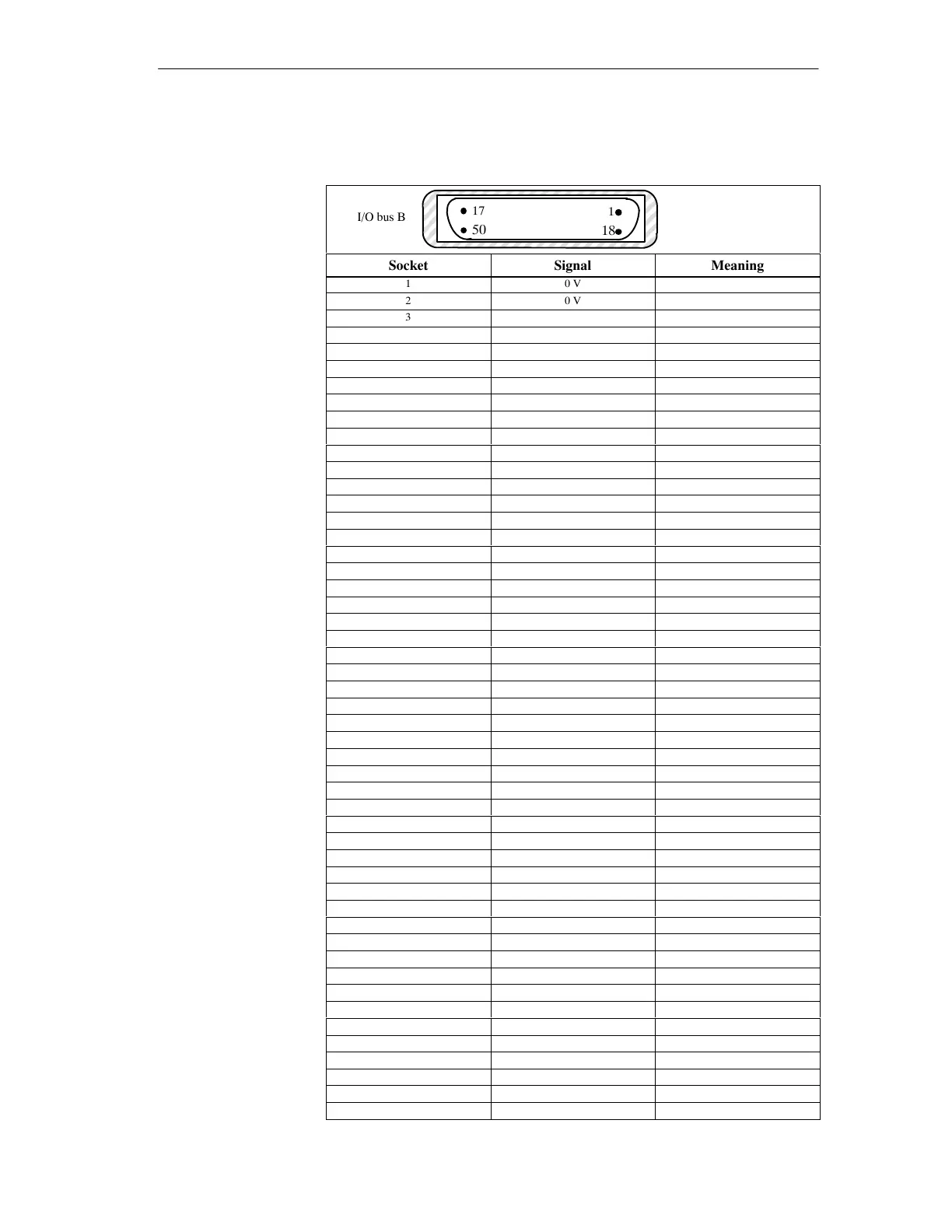

Table A-3 Pin-out 50-pole-Sub-D socket at the right side of TPM 478-2, for con-

necting I/O Bus B

ÍÍÍÍÍÍÍÍÍÍÍ

ÍÍÍÍÍÍÍÍÍÍÍ

ÍÍÍÍÍÍÍÍÍÍÍ

ÍÍÍÍÍÍÍÍÍÍÍ

50

17

1

I/O bus B

18

Socket Signal Meaning

1 0 V

2 0 V

3 +5 V Bus

4 +5 V Bus

5 +5 V Bus

6 +5 V Bus

7 +5 V Bus

8 +5 V Bus

9 PMEMR_N Peripheral Memory Read

10 PMEMW_N Peripheral Memory Write

11 0 V

12 - nc

13 PRDY_N Peripheral Ready

14 PESPA Peripheral memory A

15 - nc

16 PCPKL_N Peripheral CPU clear

17 0 V

18 INT1_N Interrupt 1

19 INT2_N Interrupt 2

20 PESPB Peripheral memory B

21 - nc

22 EANK_N One-Of-N-Check

23 0 V

24 PDB6 Peripheral Data Bus 6

25 PDB7 Peripheral Data Bus 7

26 PDB2 Peripheral Data Bus 2

27 PDB3 Peripheral Data Bus 3

28 PDB4 Peripheral Data Bus 4

29 PDB5 Peripheral Data Bus 5

30 PDB0 Peripheral Data Bus 0

31 PDB1 Peripheral Data Bus 1

32 0 V

33 0 V

34 PADB9 Peripheral Address Bus 9

35 PADB10 Peripheral Address Bus 10

36 PADB11 Peripheral Address Bus 11

37 PADB3 Peripheral Address Bus 3

38 PADB4 Peripheral Address Bus 4

39 PADB5 Peripheral Address Bus 5

40 PADB6 Peripheral Address Bus 6

41 PADB7 Peripheral Address Bus 7

42 PADB8 Peripheral Address Bus 8

43 PADB0 Peripheral Address Bus 0

44 PADB1 Peripheral Address Bus 1

45 PADB2 Peripheral Address Bus 2

46 0 V

47 - nc

48 - nc

49 - nc

50 0 V

Technical Data

Loading...

Loading...