Technical specifications

A.2 Fail-Safe CPU technical specifications

S7-1200 Functional Safety Manual

Manual, 02/2015, A5E03470344-AA

161

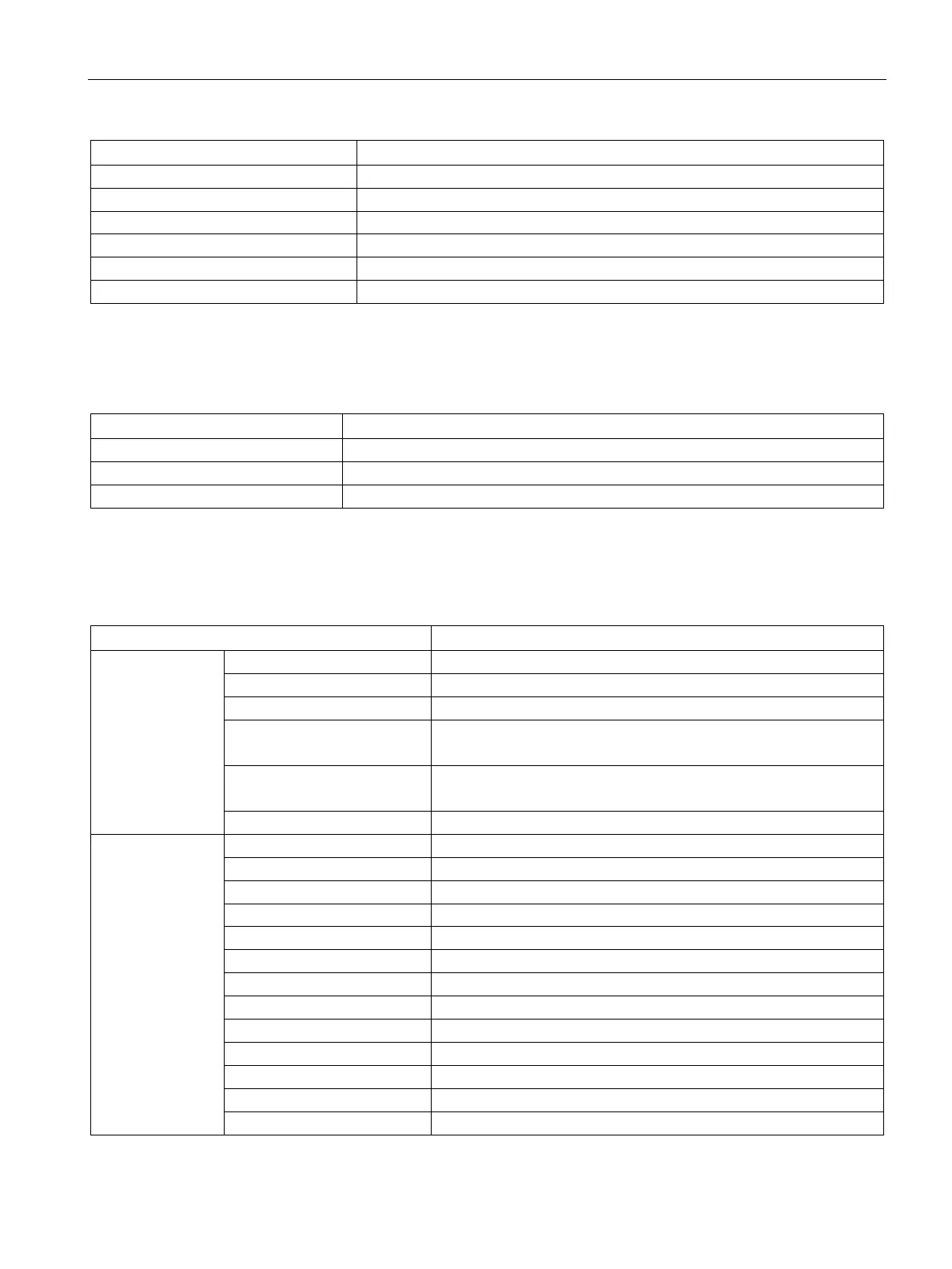

4 total with 1 ms resolution

Cyclic interrupts 4 total with 1 ms resolution

12 rising and 12 falling (16 and 16 with optional signal board)

Memory card SIMATIC Memory Card (optional)

Real time clock retention time

20 days typ./12 days min. at 40 °C (maintenance-free Super Capacitor)

The slower speed is applicable when the HSC is configured for quadrature mode of operation.

2

For CPU models with relay outputs, you must install a digital signal board (SB) to use the pulse outputs.

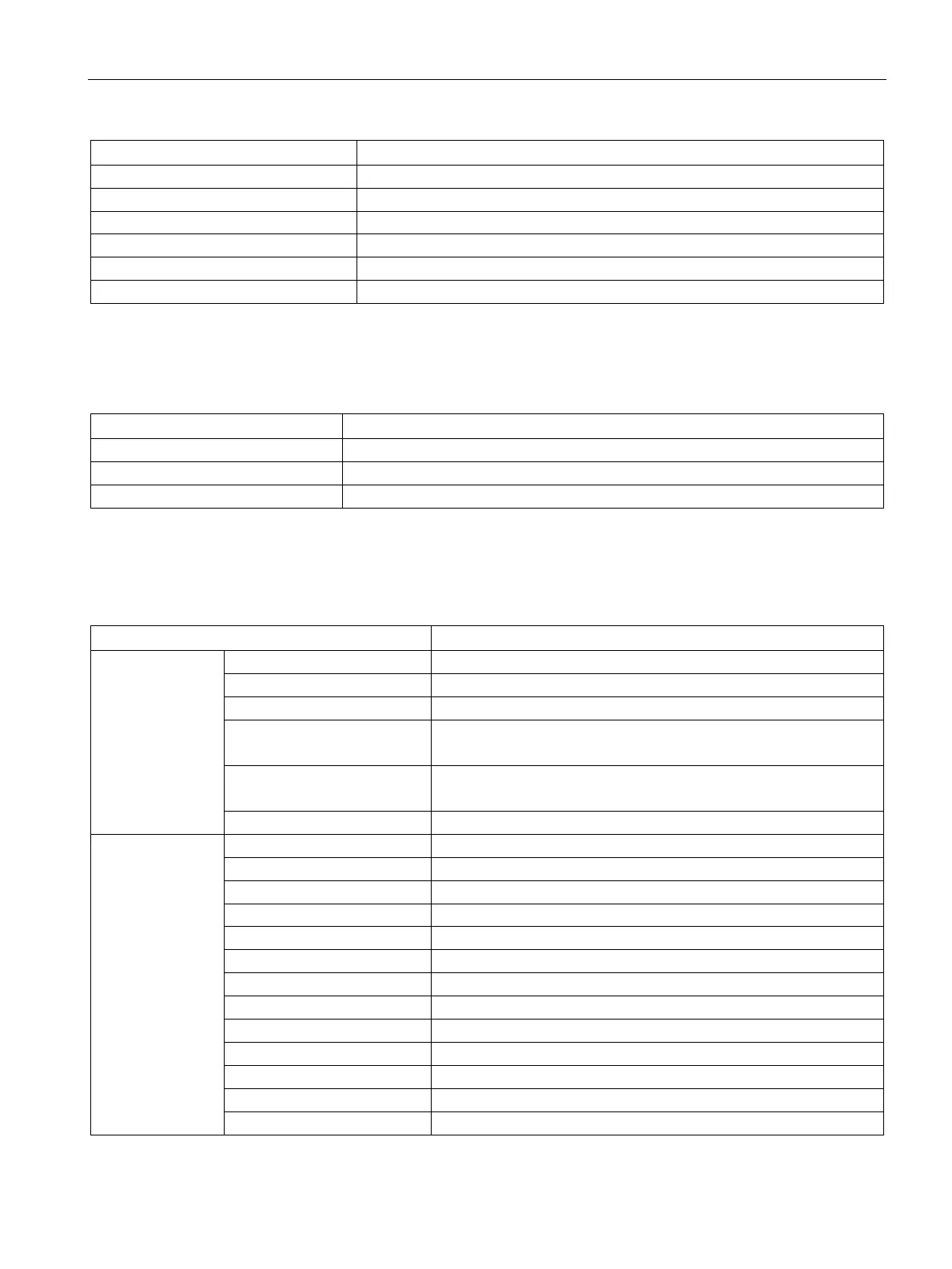

Table A- 28 Performance

Timers, counters and code blocks supported

Table A- 29 Blocks, timers and counters supported by CPU 1215FC

Blocks

Up to 1024 blocks total (OBs + FBs + FCs + DBs)

Address range for FBs, FCs,

and DBs

FB and FC: 1 to 65535 (such as FB 1 to FB 65535)

Nesting depth 16 from the program cycle or startup OB

6 from any interrupt event OB

Status of 2 code blocks can be monitored simultaneously

OBs

Hardware interrupts 50 (1 per event)

Diagnostic error interrupts

Loading...

Loading...