C-DIAS ANALOG INPUT MODULE CAI 042

Page 20 02.08.2011

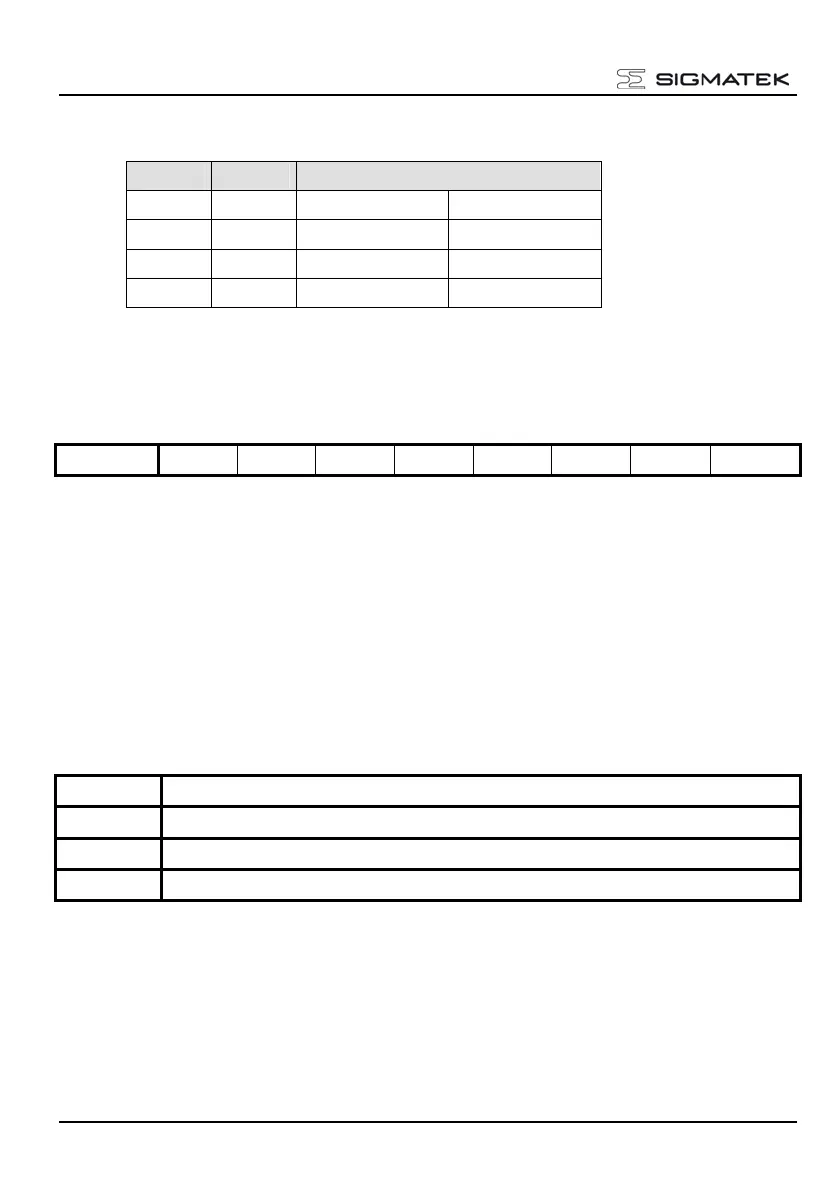

Filter table

FIL1 FIL0 Filter frequency for Filter 2

0 0 f

g

= f

Samp

/ 8 Filter 2-1

0 1 f

g

= f

Samp

/ 16 Filter 2-2

1 0 f

g

= f

Samp

/ 32 Filter 2-3

1 1 f

g

= f

Samp

/ 64 Filter 2-4

Filter 1 (fixed value filter) has a filter frequency of

f

g

= f

Samp

/ 96.

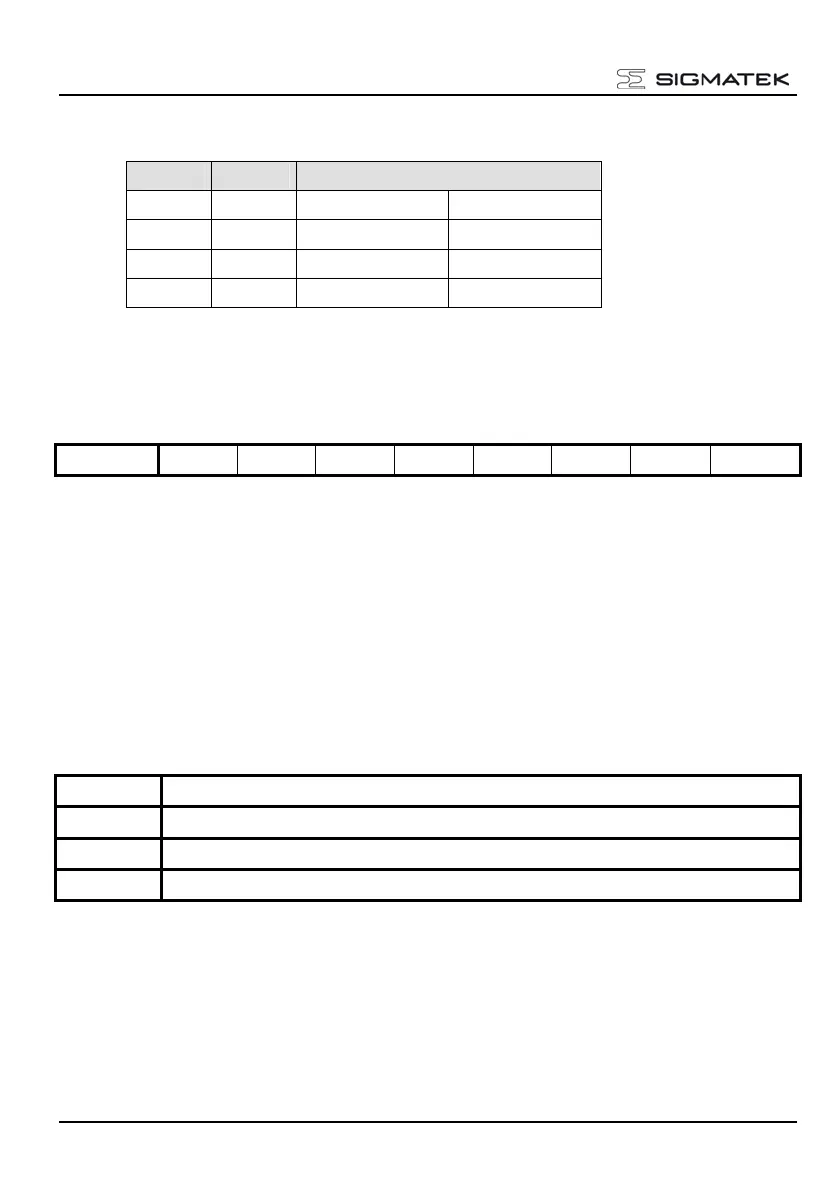

Status register for Channel x – SRx

Bit 7 6 5 4 3 2 1 0

SRx - - - - - - - SIGOF

R/W R R R

Initial Value 0 0 0 0 0 0 0 0

x ... [1..4]

• BIT 0 – SIGOV: Signal Overflow

If this bit is set, the measured value of the input signal is too high.

When cleared, the measured value is within range.

Data Register - DATAx_Py

Bit 7 6 5 4 3 2 1 0

DATAx_Py_Fz DATAx_Py_Fz [7..0]

DATAx_Py_Fz DATAx_Py_Fz [15..8]

DATAx_Py_Fz DATAx_Py_Fz [23..16]

DATAx_Py_Fz DATAx_Py_Fz [31..24]

R/W R R R R R R R R

Initial Value 0 0 0 0 0 0 0 0

x ... [1 … 4], y ... [0, 1], z ... [1, 2]

32 Bit Data register for channel x, page y and filter z.

Loading...

Loading...