Si5338-RM

Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com 59

Rev. 1.4 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • 2021

Reset value = xxxx xxxx

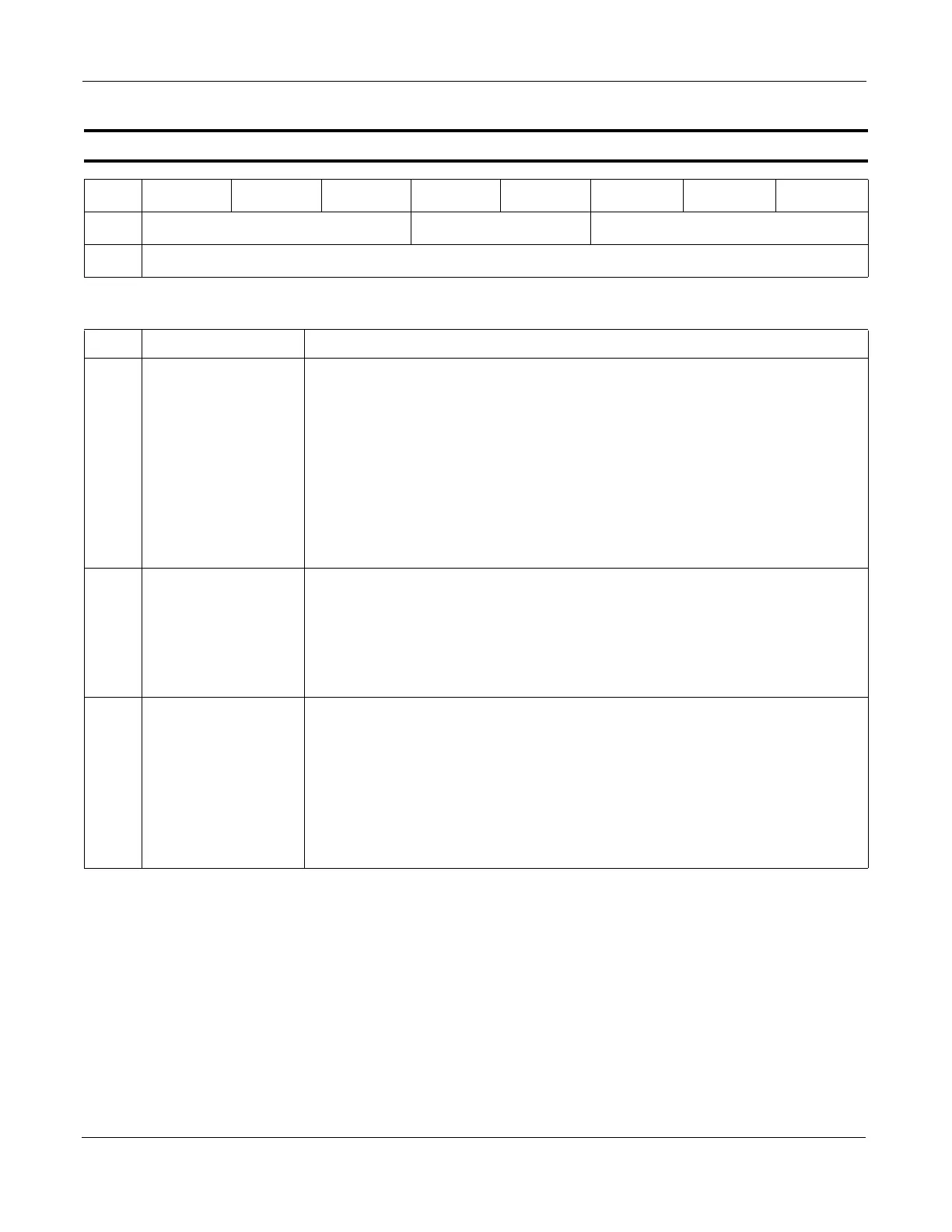

Register 29.

BitD7D6D5D4D3D2 D1 D0

Name

PFD_IN_REF[2:0] P1DIV_IN[4:3] P1DIV[2:0]

Type R/W R/W R/W

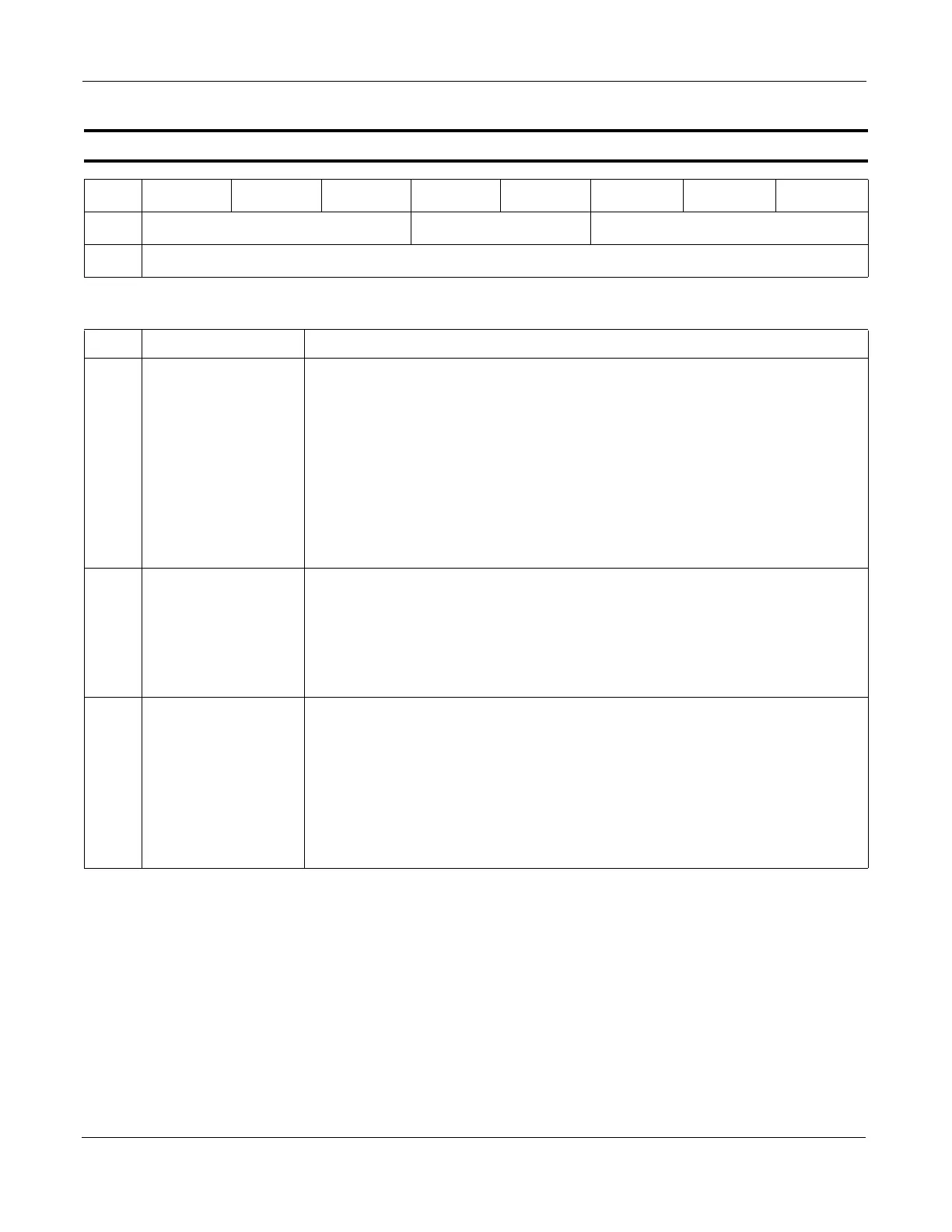

Bit Name Function

7:5 PFD_IN_REF[2:0]

Selects the input clock to be provided to the reference input of PLL Phase

Frequency Detector (PFD).

000b: P1DIV_IN selected

001b: P2DIV_IN selected

010b: P1DIV_OUT (P1 divider output) selected

011b: P2DIV_OUT (P2 divider output) selected

100b: XOCLK selected

101b: No Clock selected

110b: Reserved

111b: Reserved

4:3 P1DIV_IN[4:3]

These two bits along with reg28[4:2] create a 5-bit field that selects the input to

the P1 divider [reg29[4:3] reg28[4:2]] = P1DIV_IN[4:0].

00000b: Clock from IN,2 selected

01010b: Clock from IN3 selected

10101b: Crystal oscillator selected

All other bit values are reserved

2:0 P1DIV[2:0]

Sets the value of the P1 divider.

000b: Divide by 1

001b: Divide by 2

010b: Divide by 4

011b: Divide by 8

100b: Divide by 16

101b: Divide by 32

All other bit values are reserved.

Loading...

Loading...