3.6.14 Basic timers TIM 6/7

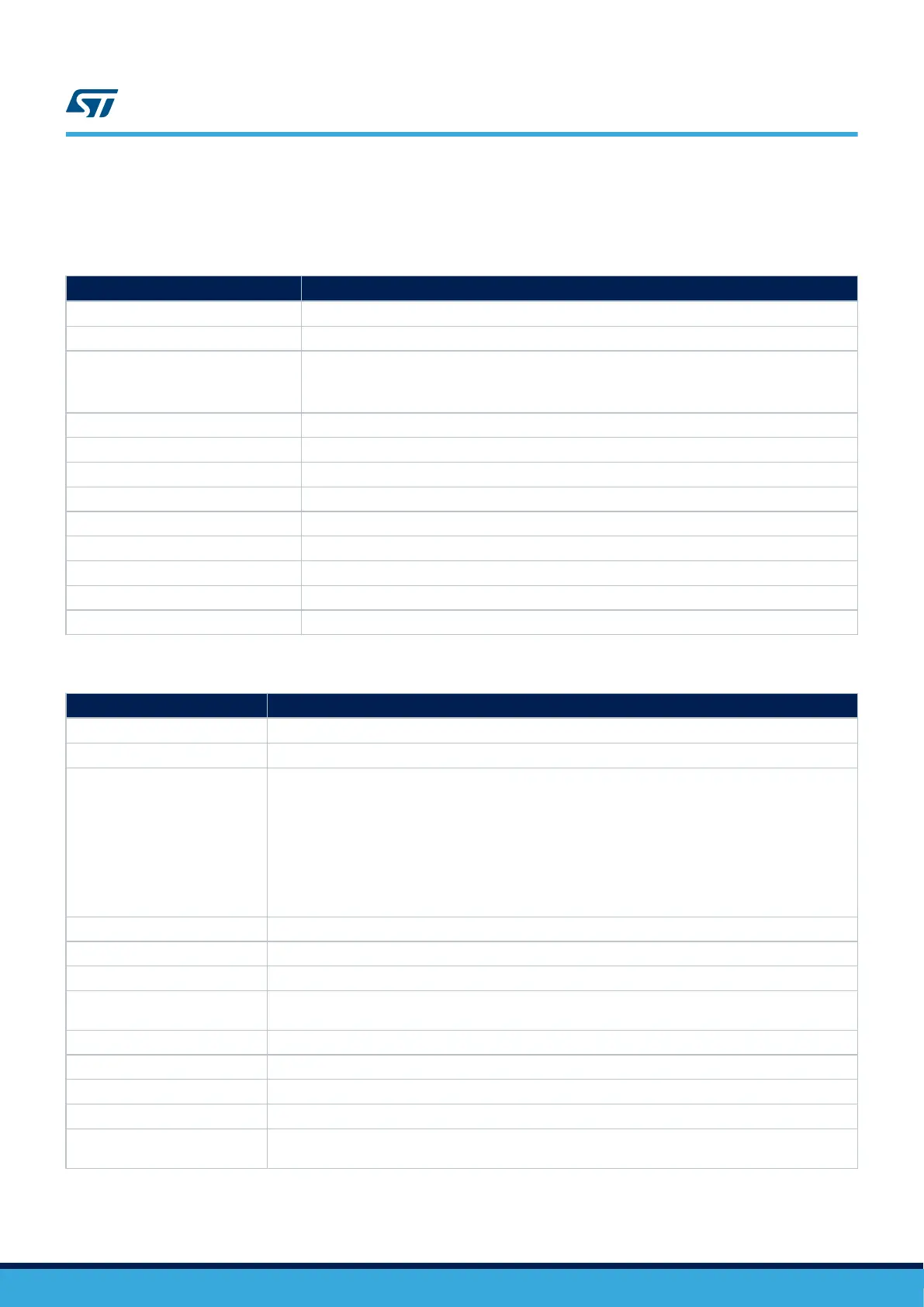

Table 65. GTIM_SM_0

SM CODE GTIM_SM_0

Description Periodical read-back of configuration registers

Ownership End user

Detailed implementation

This method must be applied to general purpose counter timer TIM6 or TIM7 configuration

registers.

Detailed information on the implementation of this method can be found in Section 3.6.5

Error reporting Refer to NVIC_SM_0

Fault detection time Refer to NVIC_SM_0

Addressed fault model Refer to NVIC_SM_0

Dependency on MCU configuration Refer to NVIC_SM_0

Initialization Refer to NVIC_SM_0

Periodicity Refer to NVIC_SM_0

Test for the diagnostic Refer to NVIC_SM_0

Multiple faults protection Refer to NVIC_SM_0

Recommendations and known limitations Refer to NVIC_SM_0

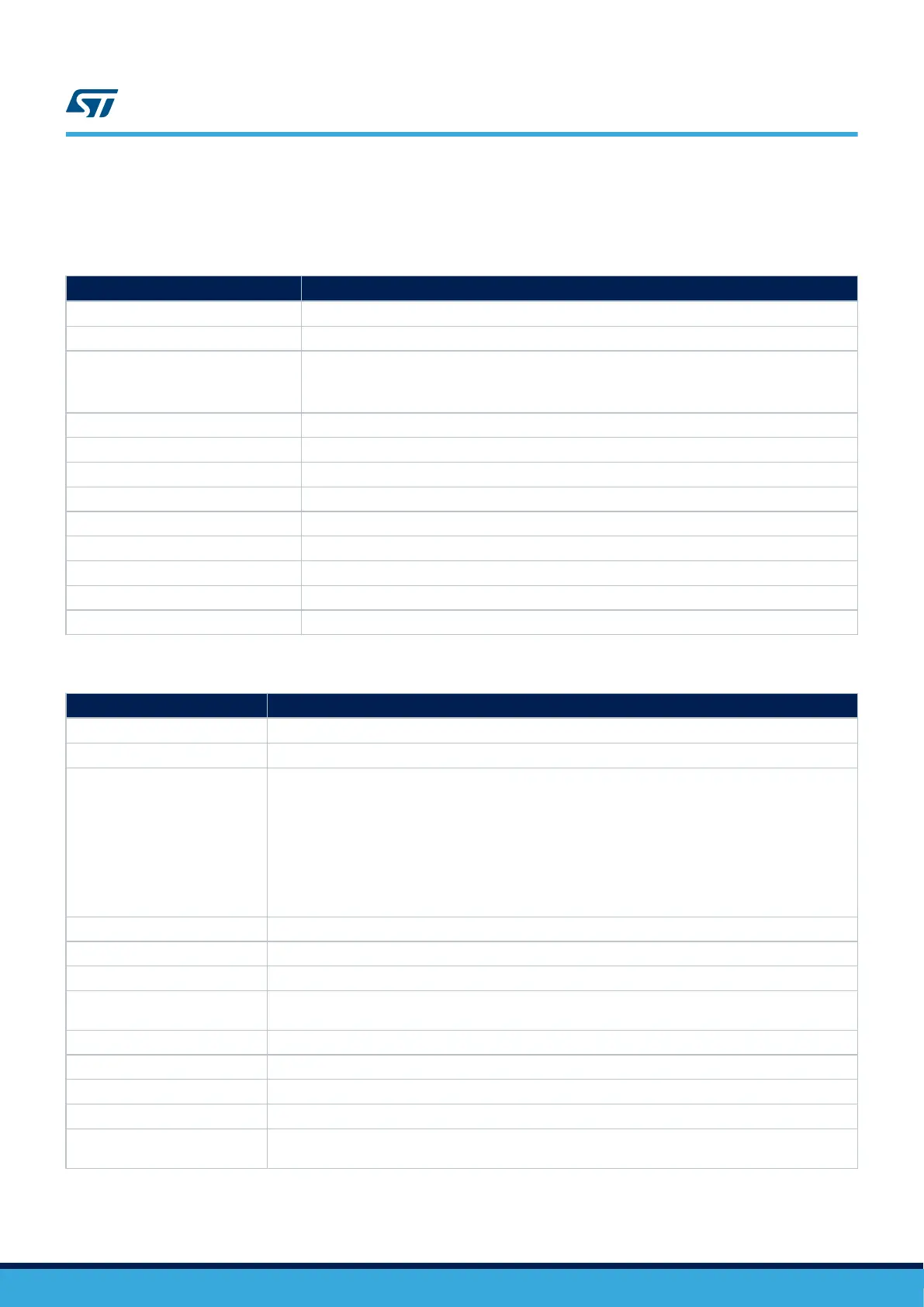

Table 66. GTIM_SM_1

SM CODE GTIM_SM_1

Description 1oo2 for counting timers

Ownership End user

Detailed implementation

This method implements via software a 1oo2 scheme between two counting resources.

The guidelines for the implementation of the method are the following:

• Two timers are programmed with same time base or frequency.

• In case of timer use as a time base: use in the application software one of the timer as time base

source, and the other one just for check. Coherence check for the 1oo2 is done at application level,

comparing two counters values each time the timer value is used to affect safety function.

• In case of interrupt generation usage: use the first timer as main interrupt source for the service

routines, and use the second timer as a “reference” to be checked at the initial of interrupt routine

Error reporting Depends on implementation

Fault detection time Depends on implementation

Addressed fault model Permanent and Transient

Dependency on MCU

configuration

None

Initialization Depends on implementation

Periodicity On demand

Test for the diagnostic Not needed

Multiple faults protection CPU_SM_0: periodical core self-test software

Recommendations and known

limitations

Tolerance implementation in timer checks is recommended to avoid false positive outcomes of the

diagnostic

UM1845

Description of hardware and software diagnostics

UM1845 - Rev 4

page 48/108

Loading...

Loading...