3.6.29 HASH processor (HASH)

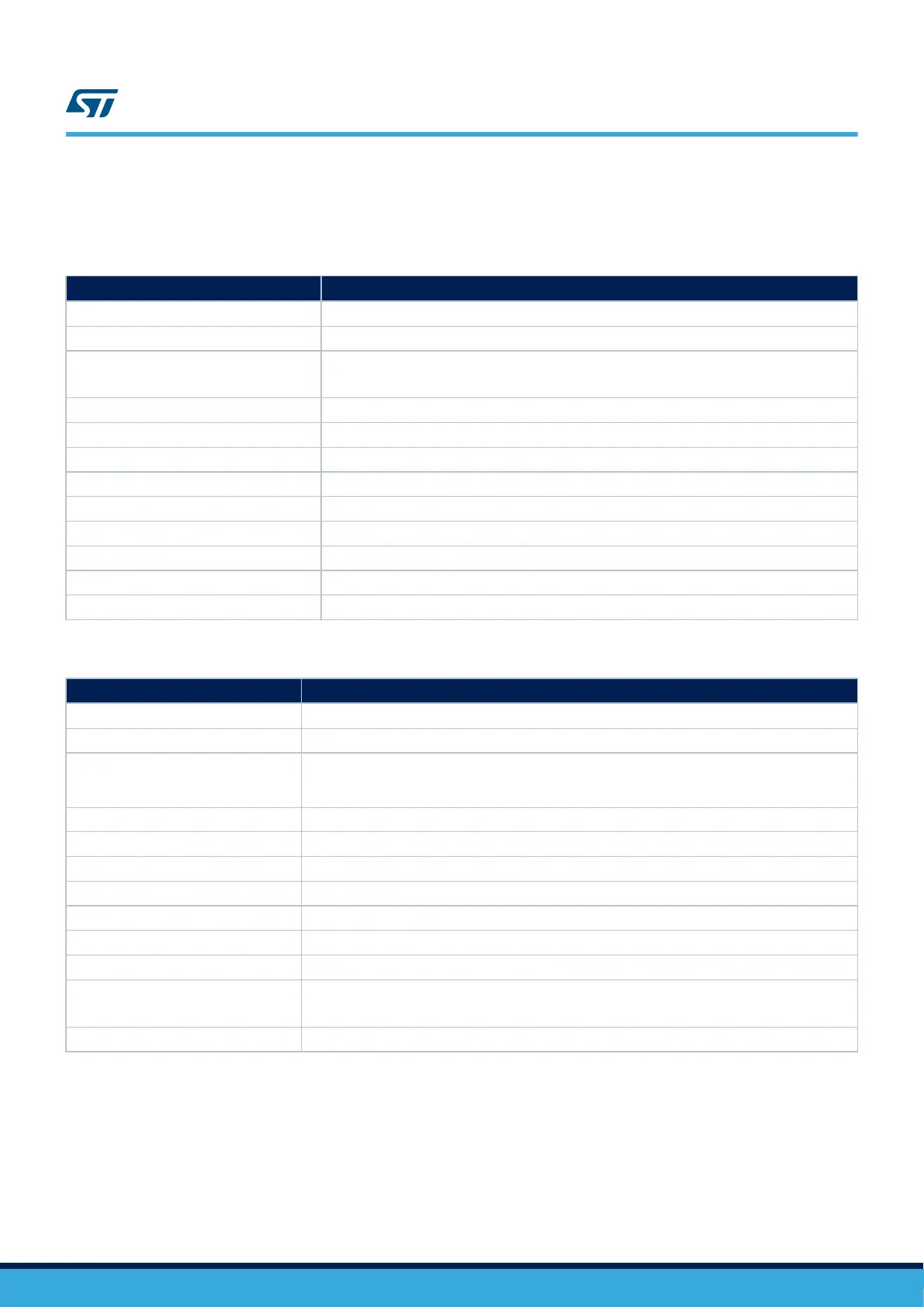

Table 110. HASH_SM_0

SM CODE HASH_SM_0

Description Periodical read-back of HASH configuration registers

Ownership End user

Detailed implementation

This method must be applied to HASH configuration registers.

Detailed information on the implementation of this method can be found in Section 3.6.5

Error reporting Refer to NVIC_SM_0

Fault detection time Refer to NVIC_SM_0

Addressed fault model Refer to NVIC_SM_0

Dependency on MCU configuration HASH module available only on specific part numbers

Initialization Refer to NVIC_SM_0

Periodicity Refer to NVIC_SM_0

Test for the diagnostic Refer to NVIC_SM_0

Multiple faults protection Refer to NVIC_SM_0

Recommendations and known limitations Refer to NVIC_SM_0

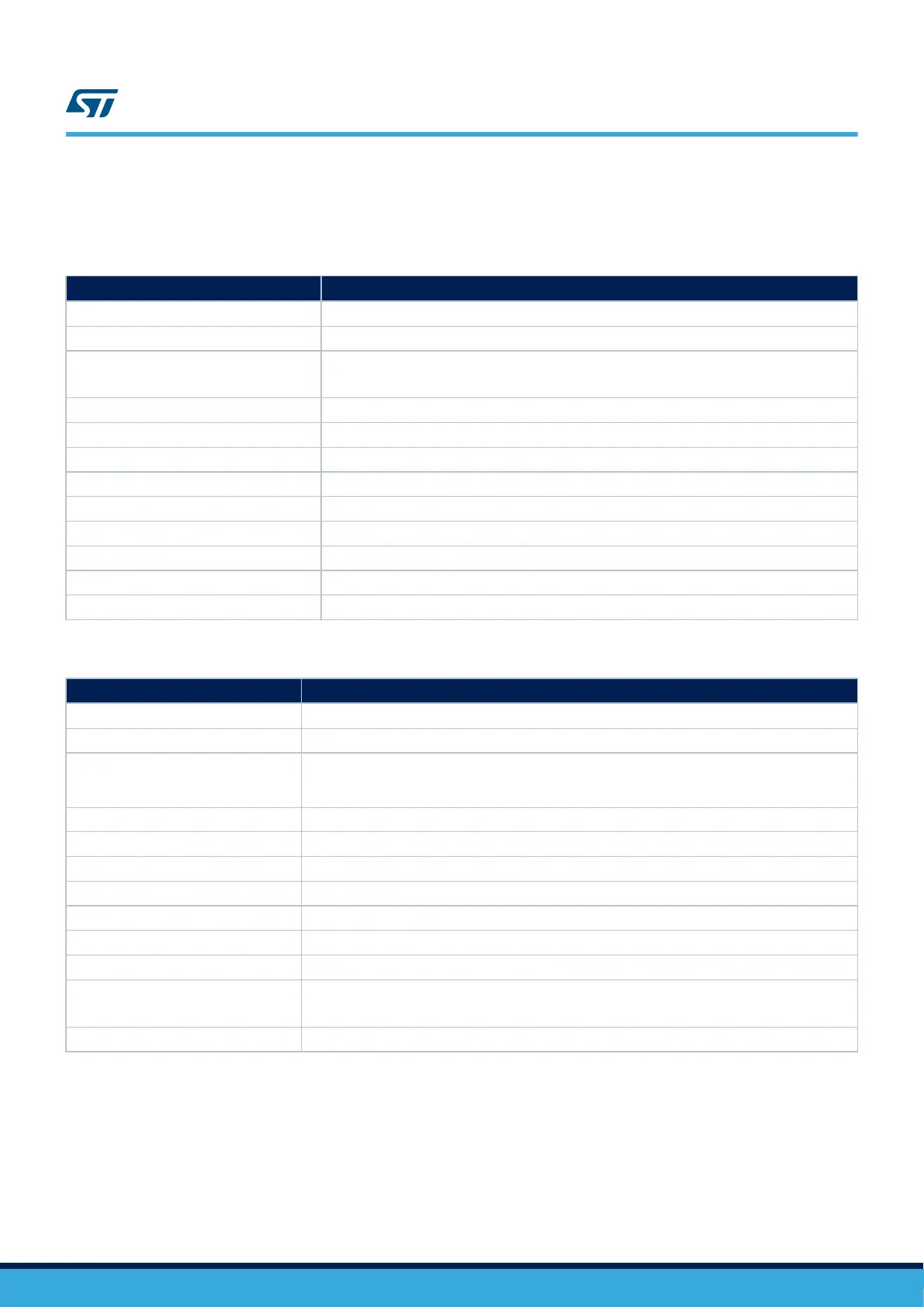

Table 111. HASH_SM_1

SM CODE HASH_SM_1

Description HASH processing collateral detection

Ownership ST

Detailed implementation

Message digest computation performed by HASH module is composed by several data

manipulations and checks. A major part of the hardware random failures affecting HASH module

will lead to algorithm violations/errors, and so to decoding errors on the receiver side

Error reporting Several error condition can happens, check functional documentation

Fault detection time Depends on peripheral configuration

Addressed fault model Permanent and Transient

Dependency on MCU configuration HASH module available only on specific part numbers

Initialization Depends on implementation

Periodicity Continuous

Test for the diagnostic N/A

Multiple faults protection

HASH_SM_0: periodical read-back of HASH configuration registers

CPU_SM_0: periodical core self-test software

Recommendations and known limitations -

Note: Hardware random failures consequences on potential security features violations are not analyzed in this

manual.

UM1845

Description of hardware and software diagnostics

UM1845 - Rev 4

page 74/108

Loading...

Loading...