Reset and power supply supervisor AN4488

18/50 AN4488 Rev 7

power on/power down reset threshold, refer to the electrical characteristics in the product

datasheets.

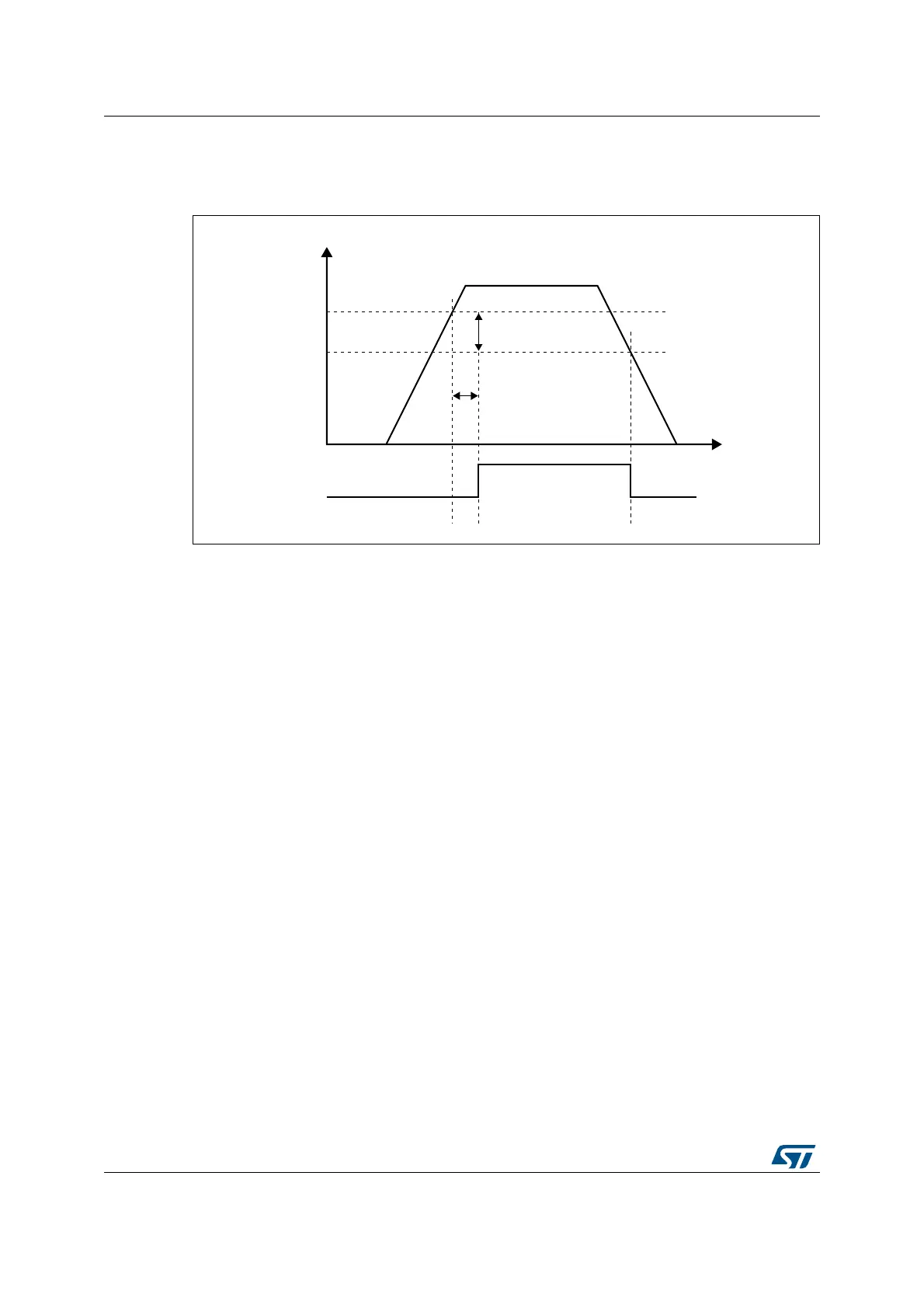

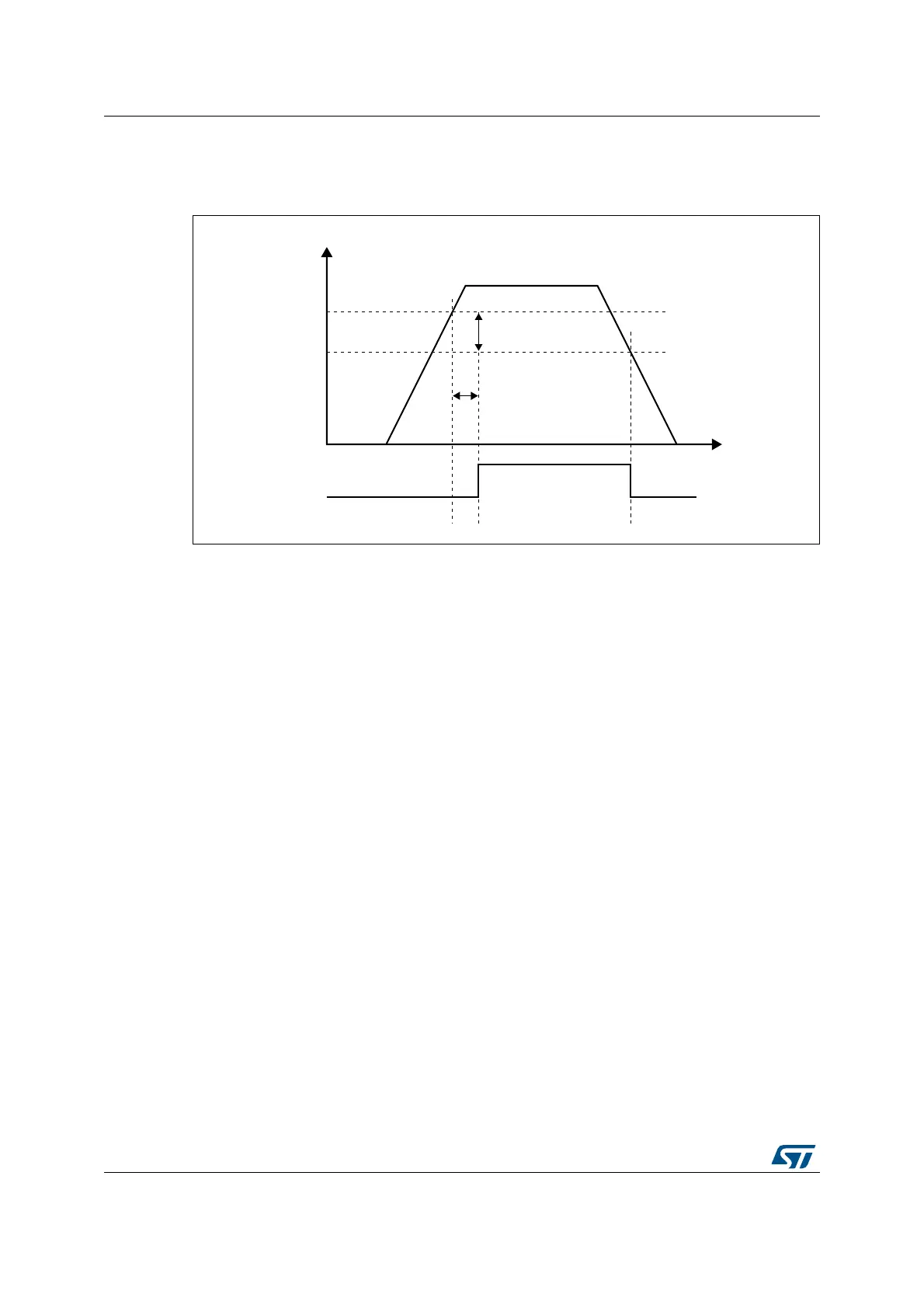

Figure 9. Power-on reset/power-down reset waveform

1. t

RSTTEMPO

is approximately 2.6 ms. V

POR/PDR

rising edge is 1.74 V (typ.) and V

POR/PDR

falling edge is

1.70 V (typ.). Refer to STM32F4xxxx datasheets for actual value.

The internal power-on reset (POR) / power-down reset (PDR) circuitry is disabled through

the PDR_ON pin. An external power supply supervisor should monitor V

DD

and should

maintain the device in reset mode as long as V

DD

is below a specified threshold. PDR_ON

should be connected to this external power supply supervisor. See

Section 3.2.1 for details.

3.2.3 Programmable voltage detector (PVD)

You can use the PVD to monitor the V

DD

power supply by comparing it to a threshold

selected by the PLS[2:0] bits in the Power control register (PWR_CR).

The PVD is enabled by setting the PVDE bit.

A PVDO flag is available, in the Power control/status register (PWR_CSR), to indicate

whether V

DD

is higher or lower than the PVD threshold. This event is internally connected to

EXTI Line16 and can generate an interrupt if enabled through the EXTI registers. The PVD

output interrupt can be generated when V

DD

drops below the PVD threshold and/or when

V

DD

rises above the PVD threshold depending on the EXTI Line16 rising/falling edge

configuration. As an example the service routine can perform emergency shutdown tasks.

6

$$

0/2

0$2

M6

HYSTERESIS

4EMPORIZATION

T

2344%-0/

2%3%4

AIB

6

0/20$2

FALLINGEDGE

6

0/20$2

RISINGEDGE

Loading...

Loading...