Package AN4488

26/50 AN4488 Rev 7

The values on the BOOT pins are latched on the 4

th

rising edge of SYSCLK after a reset. It

is up to the user to set the BOOT1 and BOOT0 pins after reset to select the required boot

mode.

Boot from User Flash mode

The application code that runs after reset is located in user flash memory.

The user flash memory in this mode is aliased to start at address 0x00000000 in boot

memory space. Upon reset, the top-of-stack value is fetched from address 0x00000000,

and code then begins execution at address 0x00000004.

Boot from System Memory mode

The system memory (not the user flash) is now aliased to start at address 0x00000000. The

application code in this case must have already been loaded into system memory.

Boot from Embedded SRAM mode

The SRAM start at address 0x00000000. When this mode is selected, the device expects

the vector table to have been relocated using the NVIC exception table and offset register,

and execution begins at the start of embedded SRAM. The application code in this case

must have already been loaded into embedded SRAM.

This last mode is usually used for Debugging.

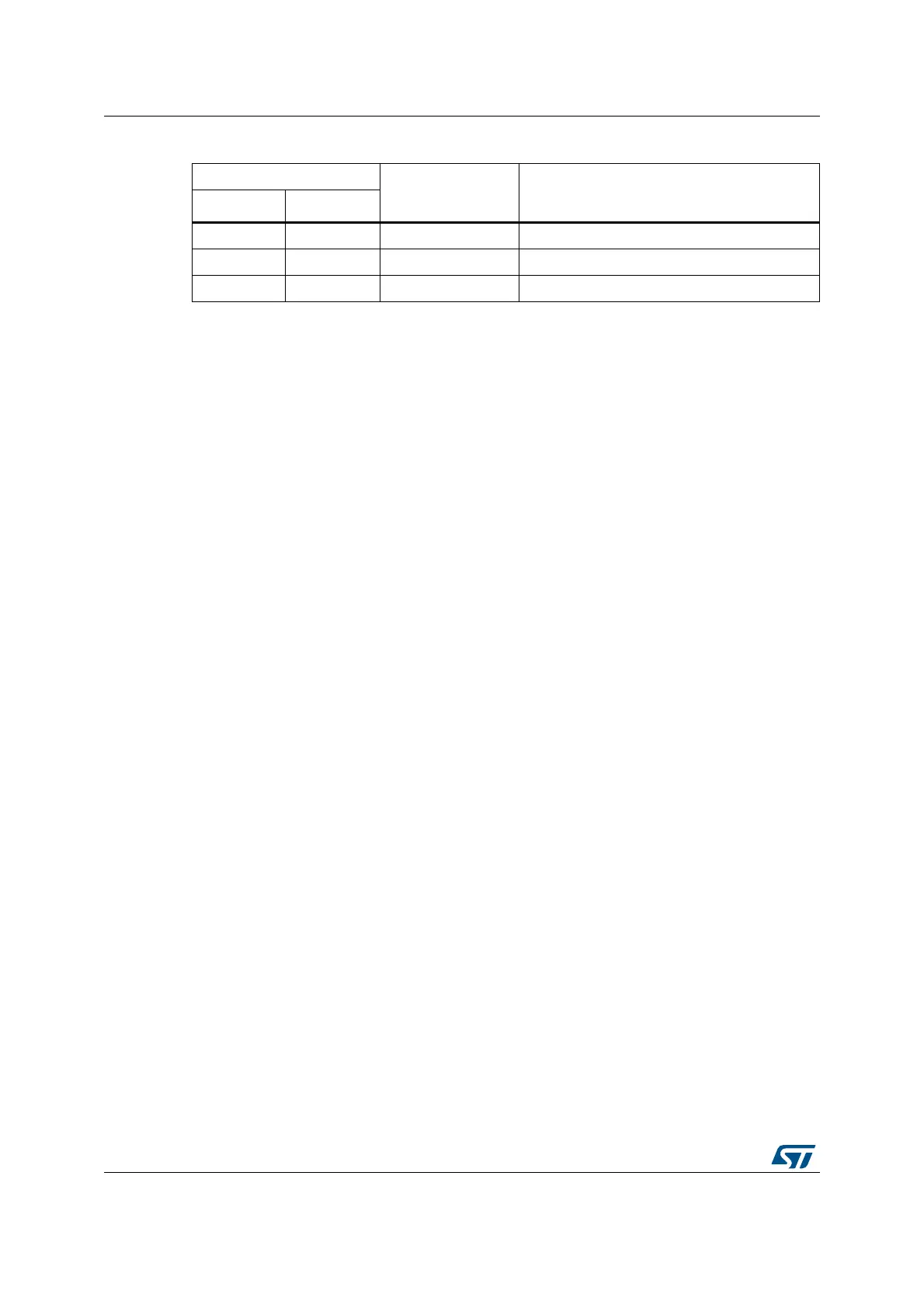

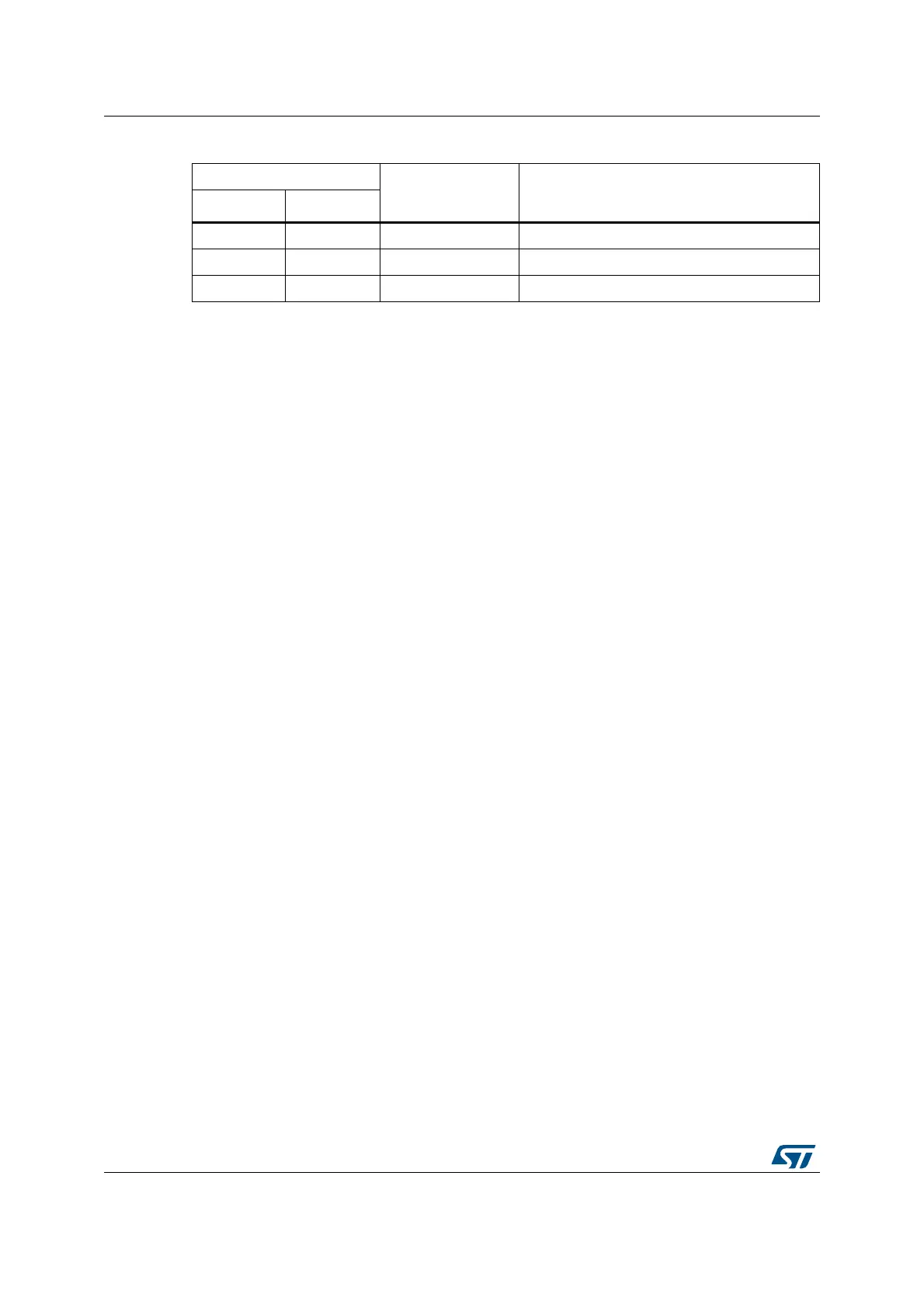

Table 6. Boot modes

BOOT mode selection pins

Boot mode Aliasing

BOOT1 BOOT0

x 0 Main Flash memory Main Flash memory is selected as boot space

0 1 System memory System memory is selected as boot space

1 1 Embedded SRAM Embedded SRAM is selected as boot space

Loading...

Loading...