DocID029918 Rev 1 29/48

AN4938 Debug management

47

5.3.3 Internal pull-up and pull-down on JTAG pins

The devices embed internal pull-ups and pull-downs to guarantee a correct JTAG behavior.

The following pins are consequently not left floating during reset and they are configured as

follows until the user software takes control of them:

• NJTRST: internal pull-up.

• JTDI: internal pull-up.

• JTMS/SWDIO: internal pull-up.

• TCK/SWCLK: internal pull-down.

If these I/Os are externally connected to a different voltage, leakage current will flow during

and after reset, until they are reconfigured by software. Special care must be taken with the

TCK/SWCLK pin, which is directly connected to the clock of some of these flip-flops, since it

should not toggle before JTAG I/O is released by the user software.”

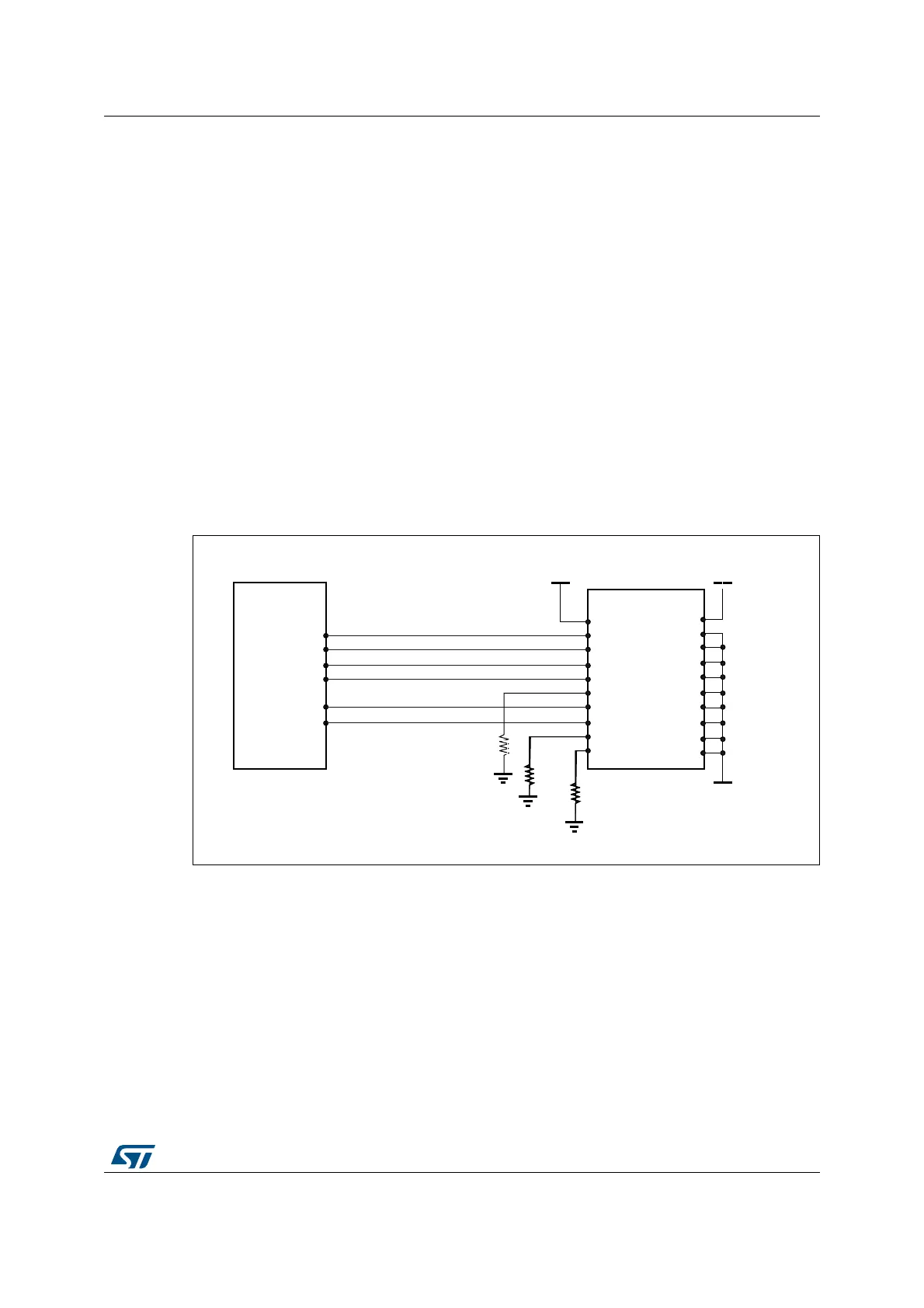

5.3.4 SWJ debug port connection with standard JTAG connector

Figure 17 shows the connection between STM32H743/753xx devices and a standard JTAG

connector.

Figure 17. JTAG connector implementation

06Y9

9

''

670+

Q-7567

-7',

-6706:',2

-7&.6:&/.

-7'2

Q567,1

975()

Q7567

7',

706

7&.

57&.

7'2

Q6567

'%*54

'%*$&.

N

N

N

&RQQHFWRU[

-7$*FRQQHFWRU&1

9

''

9

66

Loading...

Loading...