Chapter 2: Installation

2-29

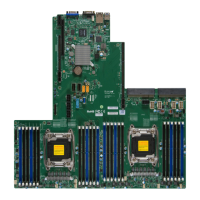

S-SGPIO

I-SGPIO2

I-SGPIO1

JIPMB1

SAN MAC

IPMI CODE

JBAT1

JPWR1

S-SATA1

S-SATA0

S-SATA3

S-SATA2

I-SATA1

I-SATA0

I-SATA3

I-SATA2

I-SATA4

I-SATA5

BIOS

LICENSE

JPI2C1

JPWR2

JPWR3

JF1

JL1

JSTBY1

JTPM1

JVRM2

JVRM1

JPME2

JVR1

JWD1

JPG1

JPB1

JI2C1

JI2C2

JPL1

SP1

LED1

LEDM1

JBT1

FANB

FANA

FAN4

FAN3

FAN2

USB4/5(3.0)

AOM CPU1 PCI-E 3.0 X16

CPU1

CPU2

P2-DIMMG1

P2-DIMMH1

P2-DIMMG2

P2-DIMMH2

ALWAYS POPULATE DIMMx1 FIRST

ALWAYS POPULATE DIMMx1 FIRST

ALWAYS POPULATE DIMMx1 FIRST

P1-DIMMA1

P1-DIMMA2

P1-DIMMB1

P1-DIMMD2

P1-DIMMC1

P1-DIMMC2

P1-DIMMD1

P2-DIMMF2

P2-DIMMF1

P2-DIMME2

P2-DIMME1

SXB1C

SXB1B:CPU1 PCI-E 3.0 X16

+ CPU2 PCI-E 3.0 X16

UID-SW

LAN2

LAN1

USB2/3(3.0)

USB0/1(3.0)

IPMI_LAN

VGA

COM1

CLOSE 1st

OPEN 1st

CLOSE 1st

OPEN 1st

IPMI

Flash

BIOS

SXB2:CPU2PCI-E 3.0 X16

SXB1A

LAN

X10DRW-i(T)

Rev. 1.01

PCH

CTRL

LED2

BMC

P1-DIMMB2

FAN1

J35

B

A

A. Internal Speaker

(Buzzer)

B. TPM/80 Port

Internal Speaker

The Internal Speaker (SP1) provides

audible indications for various beep

codes. See the table on the right for

pin denitions. Refer to the layout

below for the location of the Internal

Buzzer.

Internal Buzzer

Pin Denition

Pin# Denitions

Pin 1 Pos. (+) Beep In

Pin 2 Neg. (-) Alarm Speaker

TPM/Port 80 Header

A Trusted Platform Module/Port 80

header, located at JTPM1, provides

TPM support and Port 80 connection.

Use this header to enhance system

performance and data security. See

the table on the right for pin denitions.

TPM/Port 80 Header

Pin Denitions

Pin # Denition Pin # Denition

1 LCLK 2 GND

3 LFRAME# 4 <(KEY)>

5 LRESET# 6 +5V (X)

7 LAD 3 8 LAD 2

9 +3.3V 10 LAD1

11 LAD0 12 GND

13 SMB_CLK4 14 SMB_DAT4

15 +3V_DUAL 16 SERIRQ

17 GND 18 CLKRUN# (X)

19 LPCPD# 20 LDRQ# (X)

Loading...

Loading...