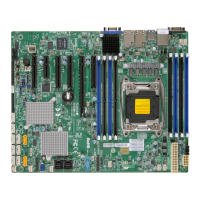

2-24

X10SRG-F Motherboard User’s Manual

A. Wake On LAN

B. System Management Bus

A

B

Legacy Wake-On-LAN Header

(JSTBY1)

The onboard LANs (LAN1 and LAN2)

do not need WOL header to sup-

port its Wake-On-LAN function. We

preserved the legacy WOL header

to provide convenience for some

embedded customers who need in-

ternal power source from the board.

See the table on the right for pin

denitions.

Wake-On-LAN

(JSTBY1)

Pin Denitions

Pin# Denition

1 +5V Standby

2 Ground

3 Wake-up

System Management Bus

(JIPMB1)

A System Management Bus header

for the IPMI slot is located at JIPMB1.

Connect the appropriate cable here

to use the IPMB I2C connection on

your system.

System Management

Bus (JIPMB1)

Pin# Denition

1 Data

2 Ground

3 Clock

4 No Connection

X10SRG-F

REV:1.01

DESIGNED IN USA

BIOS

LICENSE

MAC CODE

IPMI CODE

BAR CODE

4

1

JVRM2

JVRM1

BMC

i350

JUIDB1

FAND

FAN4

FAN3

FAN2

FAN1

FANC

FANA

FANB

JTPM1

JOH1

LE2

LE1

LEDM1

S-SATA3

S-SATA2 S-SATA1

S-SATA0

I-SATA4

I-SATA3

I-SATA5

I-SATA2I-SATA1

I-SATA0

JSTBY1

JPCIE3

JSD1

JSD2

JPW3

JPW2

JPW1

I-SGPIO2

I-SGPIO1

S-SGPIO

JIPMB1

JP3

JD1

JPL1

JPB1

JI2C2

JI2C1

JBRSET1

JBR1

JPL_LAN1

JPL_LAN0

JPL_LOM_DEV_OFF

JPG1

JPF1

JPF2

BT1

SP1

J23

USB 8/9(3.0)

USB 6/7

USB 4/5

USB 2/3

SATA

UID-SW

COM2

IPMI_LAN

VGA

CPU SLOT3 PCI-E 3.0 X8(IN X16)

SXB2A

SXB1A

JBT1

PWR

JF1

ON

RST

2

NIC

1

NIC

FF

OH

LEDLED

PWRHDDXNMI

DIMMB2

DIMMA1

DIMMB1

DIMMA2

LAN1

LAN2

COM1

USB 0/1(3.0)

Loading...

Loading...