DWC ADC 12b5M SAR, TSMC180 IP Databook

April 2012 Synopsys, Inc. 13-30

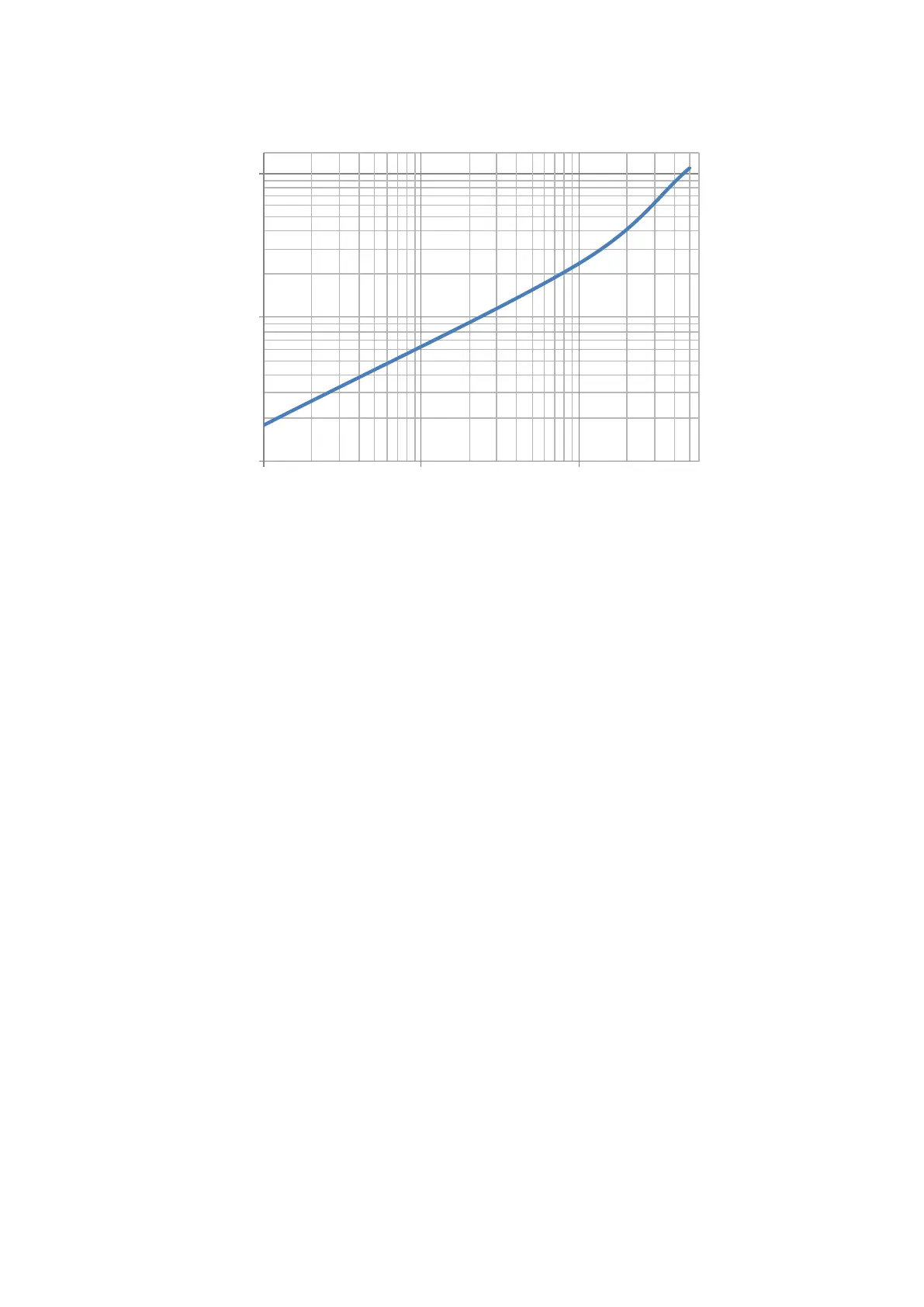

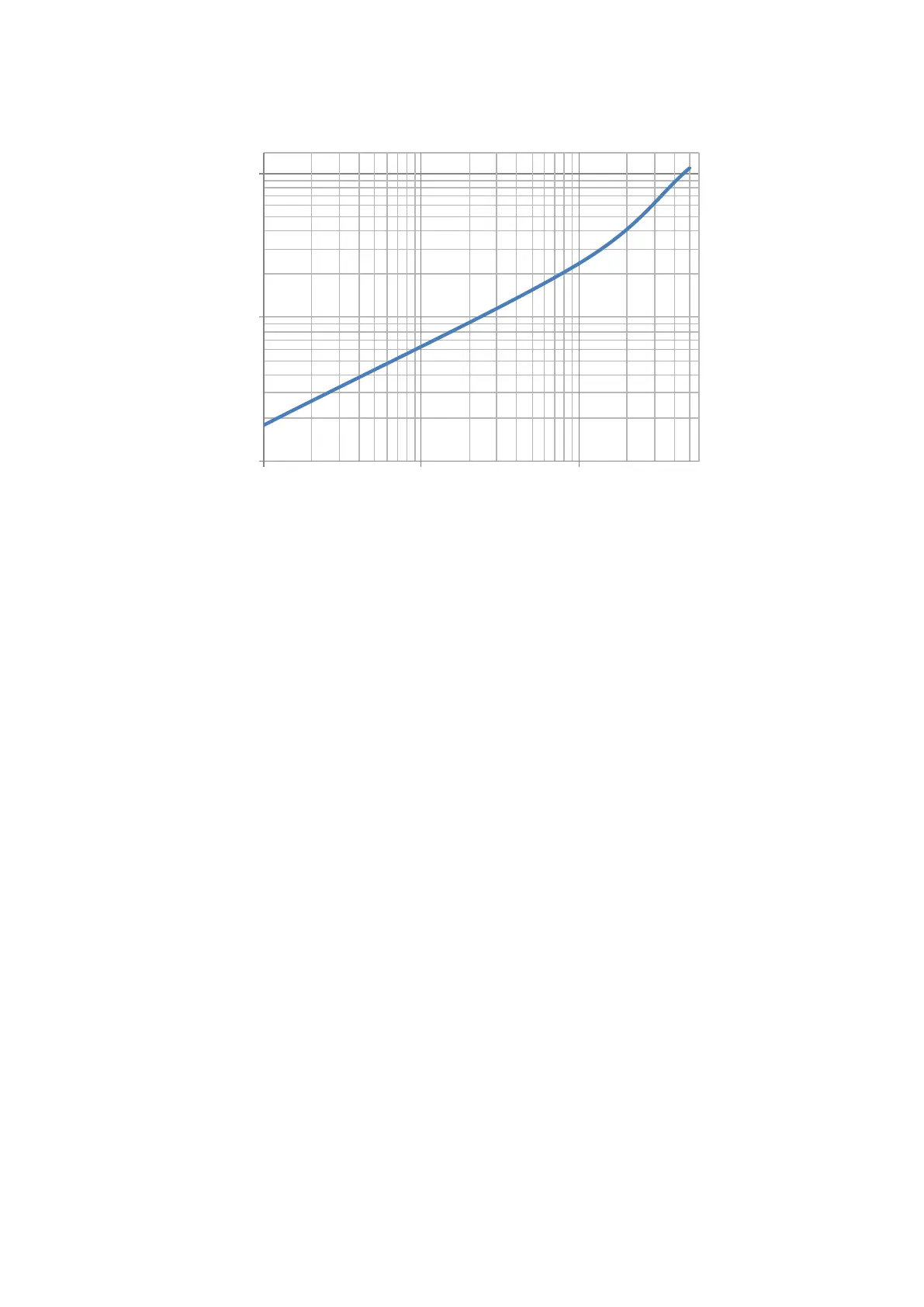

Figure 1 – ADC current consumption (single ended mode).

The current consumption presented in the previous figure is for the situation where the ADC

is operating in successive conversion mode (soc always set to high, check section 7 for

more detail).

If the ADC is waiting for a new conversion to start (soc set to low and eoc set to high), the

current consumption during this period will be greatly reduced. This can be an interesting

feature if the ADC is operating in single conversion mode (check section 7 for more detail),

which means that soc signal will only be set to high from time to time. The effective current

consumption reduction will depend on the time period left between each conversion cycle.

Please check the current consumption while the ADC is waiting for a new conversion cycle

(soc set to low and eoc set to high), in power supply requirements section in the

specifications table.

Internal Voltage Regulator

The IP includes an internal voltage regulator to generate a clean internal 1.8V power supply

(dvdd_ldo).

In case there is a clean external 1.8V power supply available for ADC use, the internal

voltage regulator can be bypassed by setting enldo=L and connecting dvdd_ldo pin to the

clean external 1.8V power supply.

ADC clock frequency (kHz)

Loading...

Loading...