DWC ADC 12b5M SAR, TSMC180 IP Databook

April 2012 Synopsys, Inc. 5-30

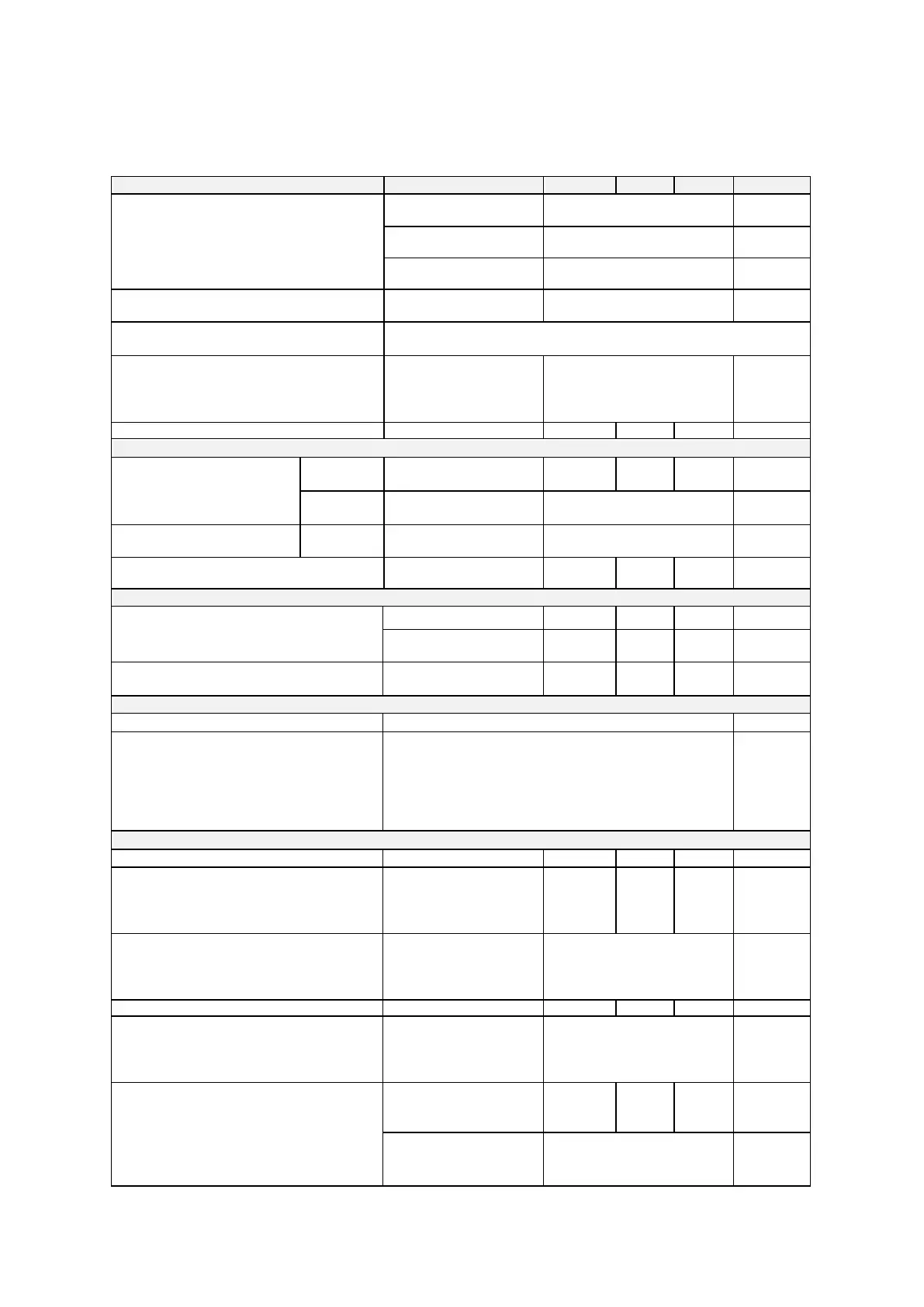

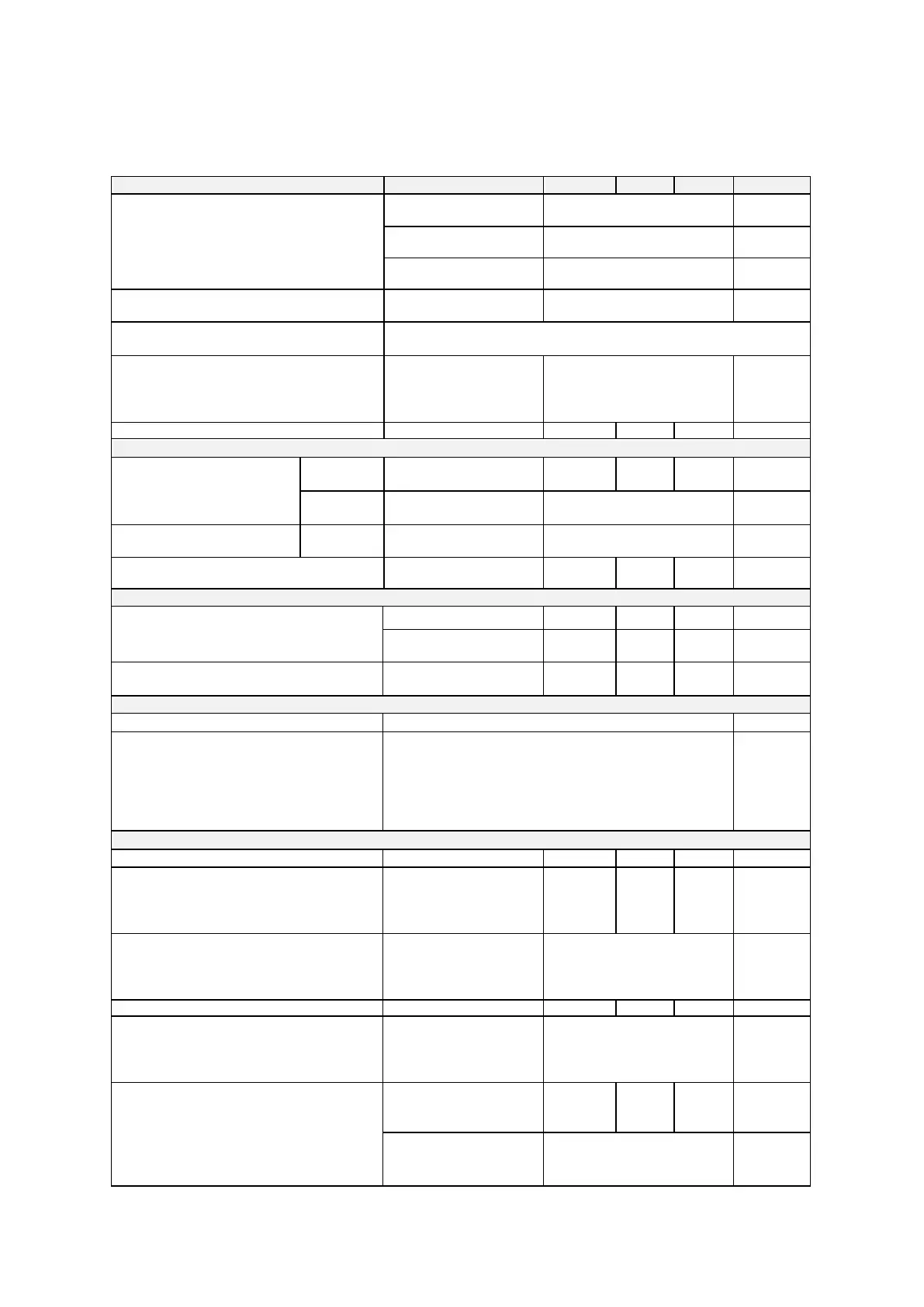

4 Specifications

TSMC 180nm G CMOS, w ith

3.3V IO devices

Minimum metal stack

supported

Metal stack available in

DWDL

(TSMC) TCB018GBWP7T Rev. 270a

TSMC 180nm Core Library

selres=11

selres=10

selres=01

selres=00

Input signal common mode

(only for differential mode)

Input sampling capacitance (C

S

)

1

No parasitic

capacitances included

Positive reference voltage (vrefp)

Negative reference voltage (agndref)

Unsigned Binary:

Bottom Scale: b11..b0=0h

Top Scale (selres=11): b11..b0=FFFh

Top Scale (selres=10): b11..b2=3FFh

Top Scale (selres=01): b11..b4=FFh

Top Scale (selres=00): b11..b6=3Fh

Input clock frequency (fclk)

selres=11

selres=10

selres=01

selres=00

selres=11

selres=10

selres=01

selres=00

selres=11

selres=10

selres=01

selres=00

From enadc=L, enldo=L

To enadc=L, enldo=H

(LDO start-up – tup_ldo)

From enadc=L,enldo=H

To enadc=H, enldo=H

(ADC start-up – tup_adc)

Loading...

Loading...