DWC ADC 12b5M SAR, TSMC180 IP Databook

April 2012 Synopsys, Inc. 6-30

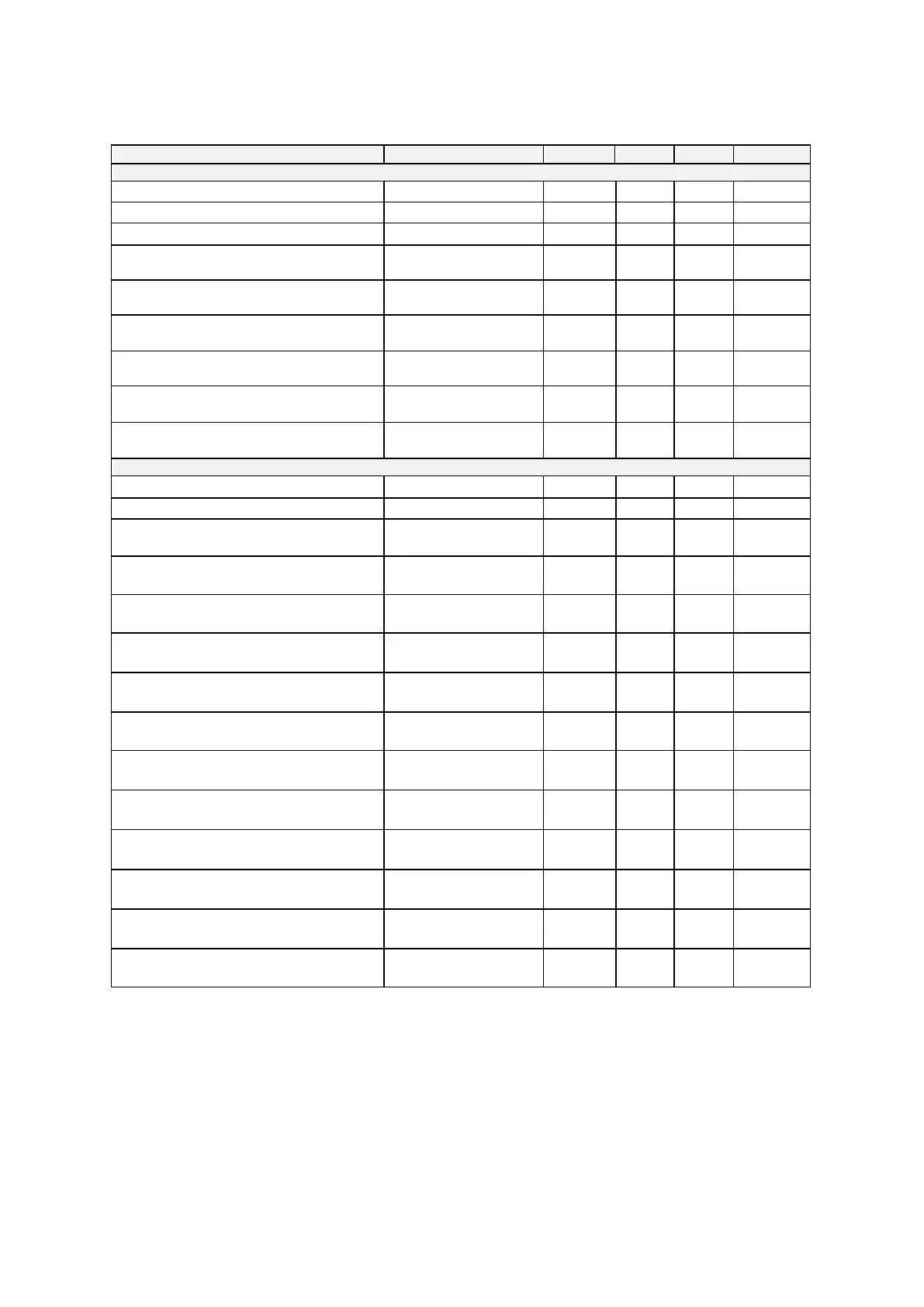

Timing Characteristics (Continued)

clk falling edge to sampling delay (tsd)

soc setup time before clk rising edge (tsocst)

soc hold time after clk rising edge (tsochld)

clk rising edge to eoc rising edge delay time

(teocr)

clk rising edge to eoc falling edge delay time

(teocf)

Valid data out delay after eoc rising edge

(tdata)

Valid serial data output delay after clk falling

edge (tdatas)

loadcal hold time after clk falling edge

(tloadcalhold)

loadcal setup time before clk rising edge

(tloadcalsetup)

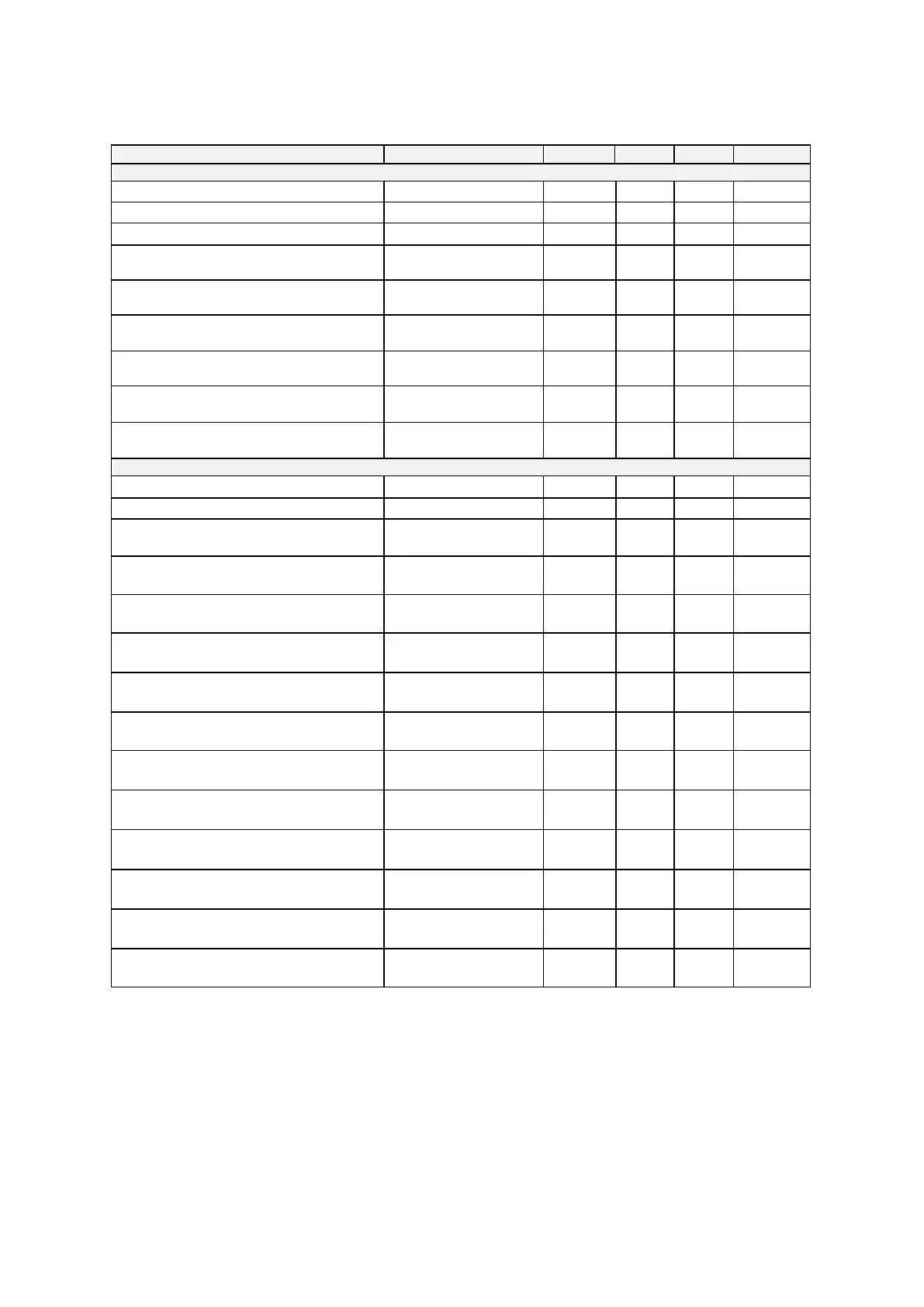

Power Supply Requirements

Current Consumption, Fs=5MSPS

1,3

avdd

dvdd

enadc=H, soc=H, seldiff=H

Current Consumption, Fs=1MSPS

1,3

avdd

dvdd

enadc=H, soc=H, seldiff=H

Current Consumption, Fs=10kSPS

1,3

avdd

dvdd

enadc=H, soc=H, seldiff=H

Current Consumption, Fs=5MSPS

1,3

avdd

dvdd

enadc=H, soc=H, seldiff=L

Current Consumption, Fs=1MSPS

1,3

avdd

dvdd

enadc=H, soc=H, seldiff=L

Current Consumption, Fs=10kSPS

1,3

avdd

dvdd

enadc=H, soc=H, seldiff=L

Current Consumption, Fs=5MSPS

2,3

avdd

dvdd

enadc=H, soc=L, seldiff=x

Current Consumption, Fs=1MSPS

2,3

avdd

dvdd

Current Consumption, Fs=10kSPS

2,3

avdd

dvdd

Pow er down Current Consumption

3

avdd

dvdd

enadc=L, enldo=L, dislvl=H

(deep power down mode)

Pow er down Current Consumption

3

avdd

dvdd

enadc=L, enldo=L, dislvl=L

(power down mode)

Pow er down Current Consumption

3

avdd

dvdd

enadc=L, enldo=H, dislvl=L

(standby mode)

Note 1 – Successiv e conv ersion mode (soc signal alway s set to high, check section 7)

Note 2 – soc signal set to low, waiting f or a conversion (check section 7)

Note 3 – avdd current consumption includes current consumption through vrefp

Loading...

Loading...