50 Network Circuitry TB9100 Reciter Service Manual

© Tait Electronics Limited January 2006

■ asynchronous SRAM

■ synchronous SRAM

■ synchronous burst SRAM

■ asynchronous flash EPROM

■ synchronous burst flash EPROM

■ standard EPROM

■ standard DRAM

■ fast page DRAM

■ EDO DRAM

■ SDRAM

■ most types of bus interfaced peripheral chips, when connected as

memory mapped devices

UPMA is used to control accesses to SDRAM while the GPCM is used to

control accesses to the flash EPROM and the DSP chip, which is classified

as a bus interfaced peripheral. UPMB is not used in the ASIF design.

Each chip select output, CS[0..7]

, has a memory controller assigned to it (see

Tabl e 5 .7) according to the requirements of the device selected by that chip

select. The assignment is controlled via internal MPC registers, which also

allocate a particular address range to a device and sets other parameters such

as address type, bus width, parity enable and write protect.

General-Purpose

Chip Select Machine

The general-purpose chip select machine (GPCM) is normally used for

controlling simple asynchronous memories such as the flash EPROM. It is

also used for controlling the accesses to the DSP host port (see “Host Port

Interface (HPI)” on page 69) and a software strobe output. Hence, the

GPCM is assigned to handle the CS0

, CS2 and CS3 chip select lines.

The GPCM also controls the write enable (WE0

) and read enable (OE)

strobes to the flash EPROM and DSP.

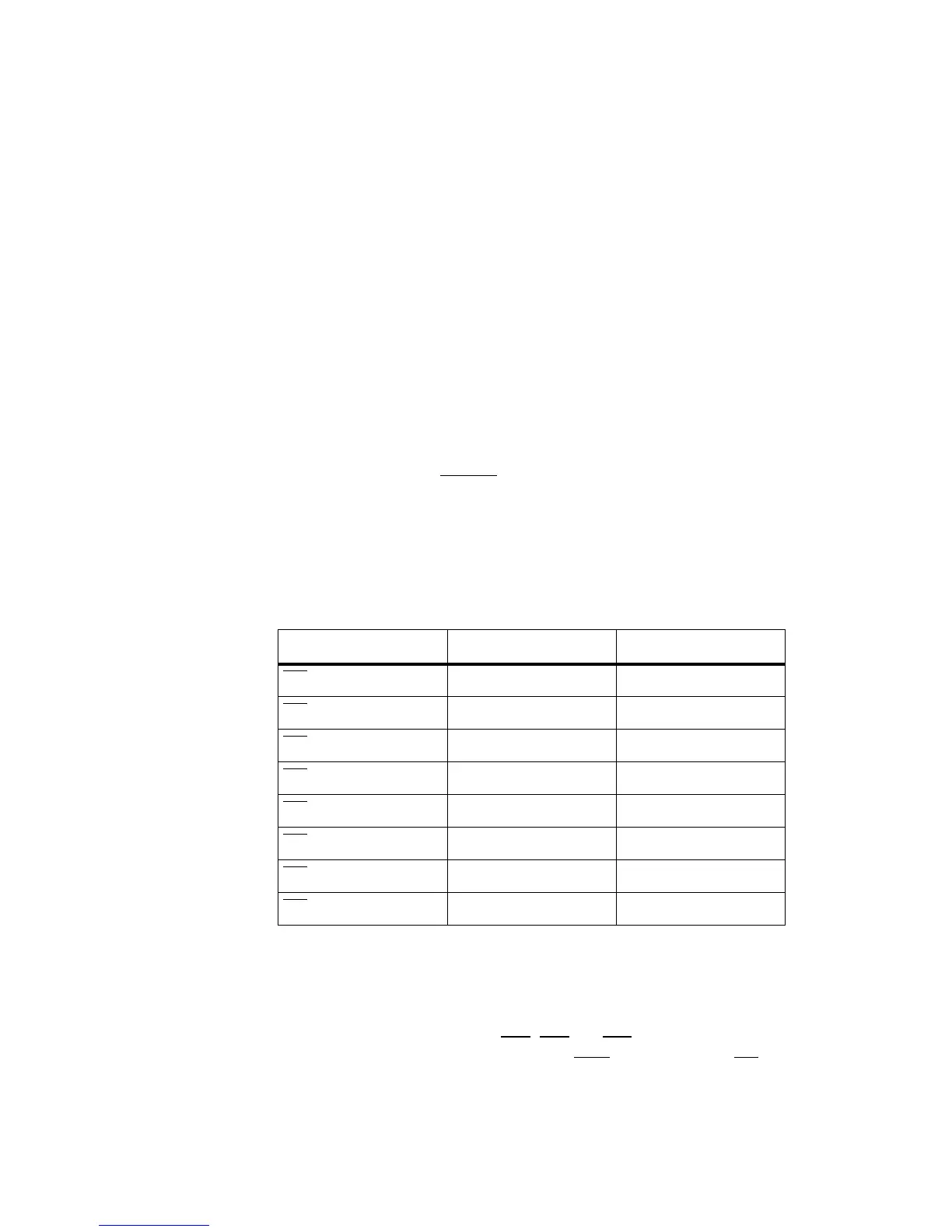

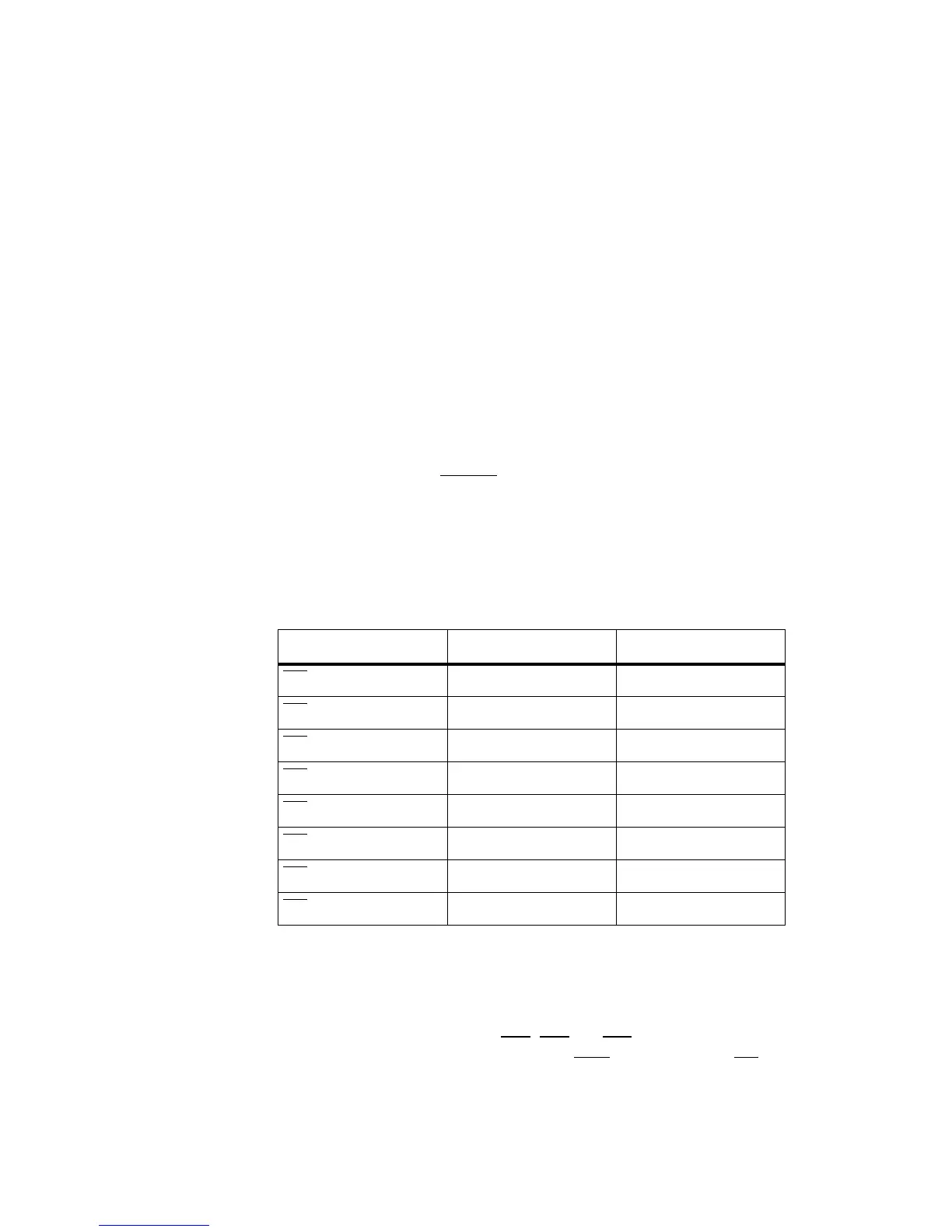

Table 5.7 Chip Select Allocation

Chip Select Output Memory Controller Device

CS0 GPCM Flash EPROM

CS1

UPMA SDRAM

CS2

GPCM DSP

CS3

GPCM software test strobe

CS4

none none

CS5

none none

CS6

none none

CS7

none none

Loading...

Loading...