ME910G1 HW Design Guide

1VV0301593 Rev.3 Page 30 of 97 2020-03-24

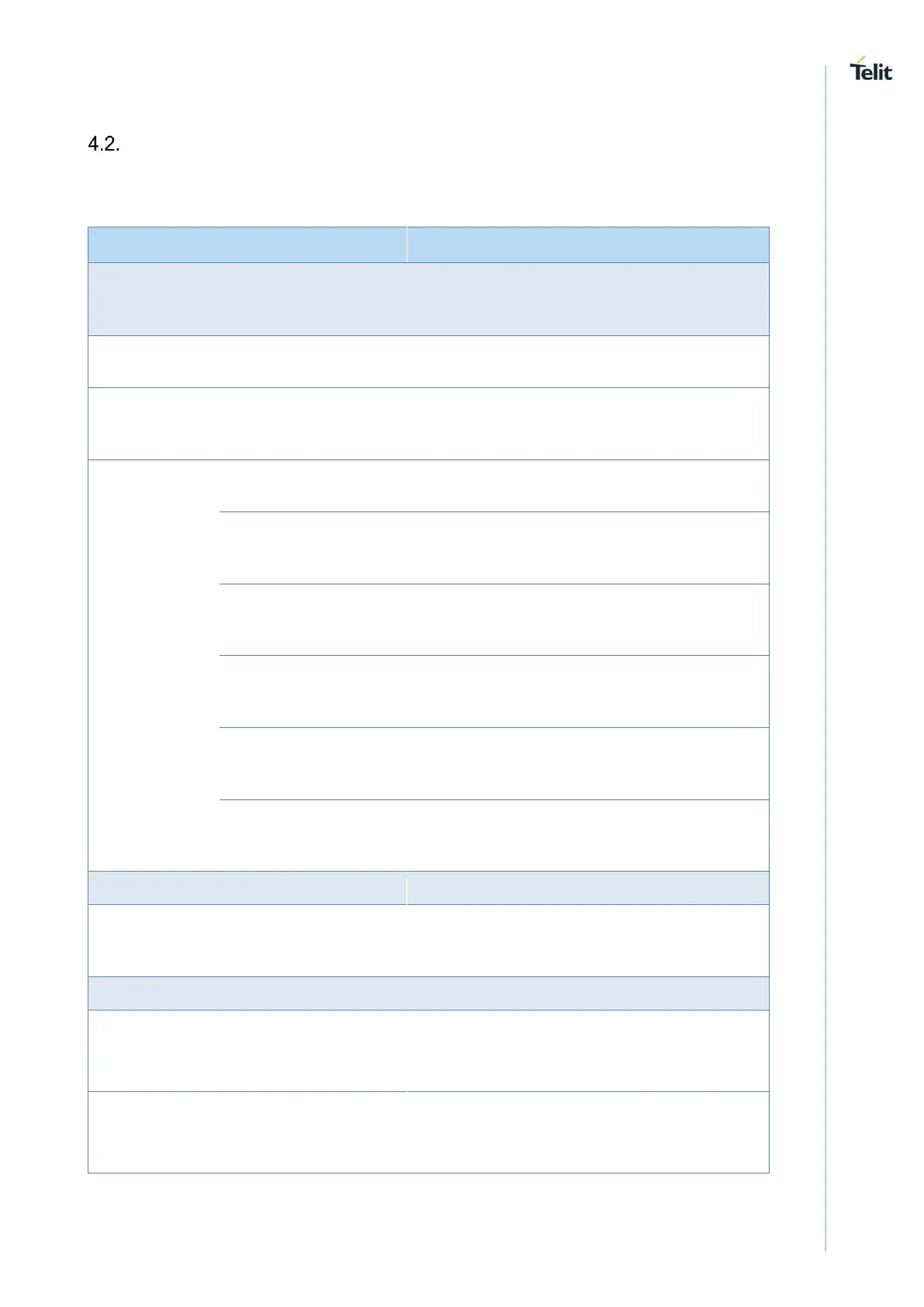

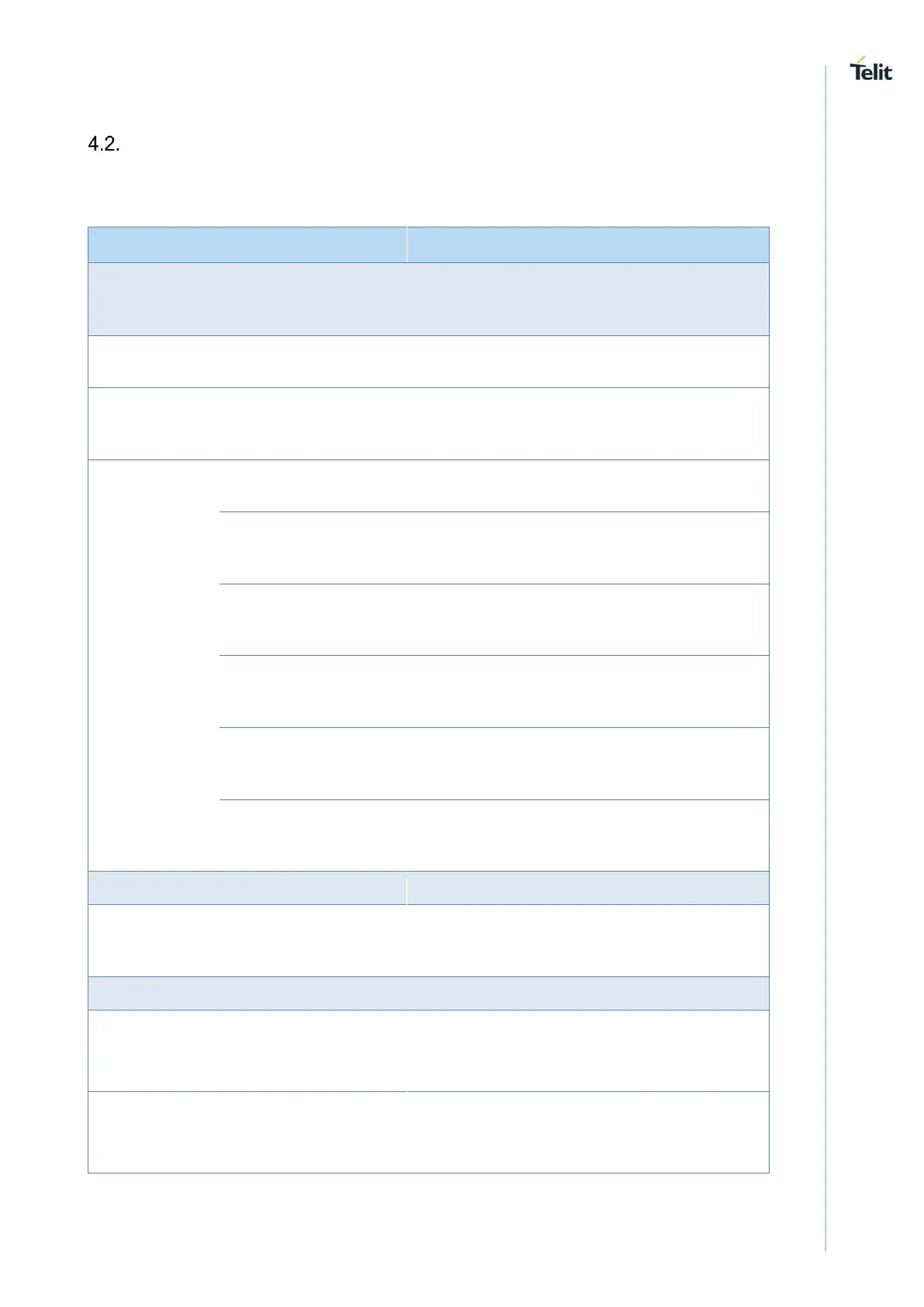

Power Consumption

Preliminary data

*Based on chipset reference data

Normal mode: full functionality of the module

Disabled TX and RX; module is not

registered on the network

Paging cycle #256 frames (2.56s DRx cycle)

81.92s eDRx cycle length (PTW=2.56s,

DRX=1.28s)

327.68s eDRx cycle length (PTW=2.56s,

DRX=1.28s)

655.36s eDRx cycle length (PTW=2.56s,

DRX=1.28s)

1310.72s eDRx cycle length (PTW=2.56s,

DRX=1.28s)

2621.44s eDRx cycle length (PTW=2.56s,

DRX=1.28s)

No current source or sink by any connected

pin

TX=0dBm, BW=10MHz, Max Throughput

375Kbps (DL)

Loading...

Loading...