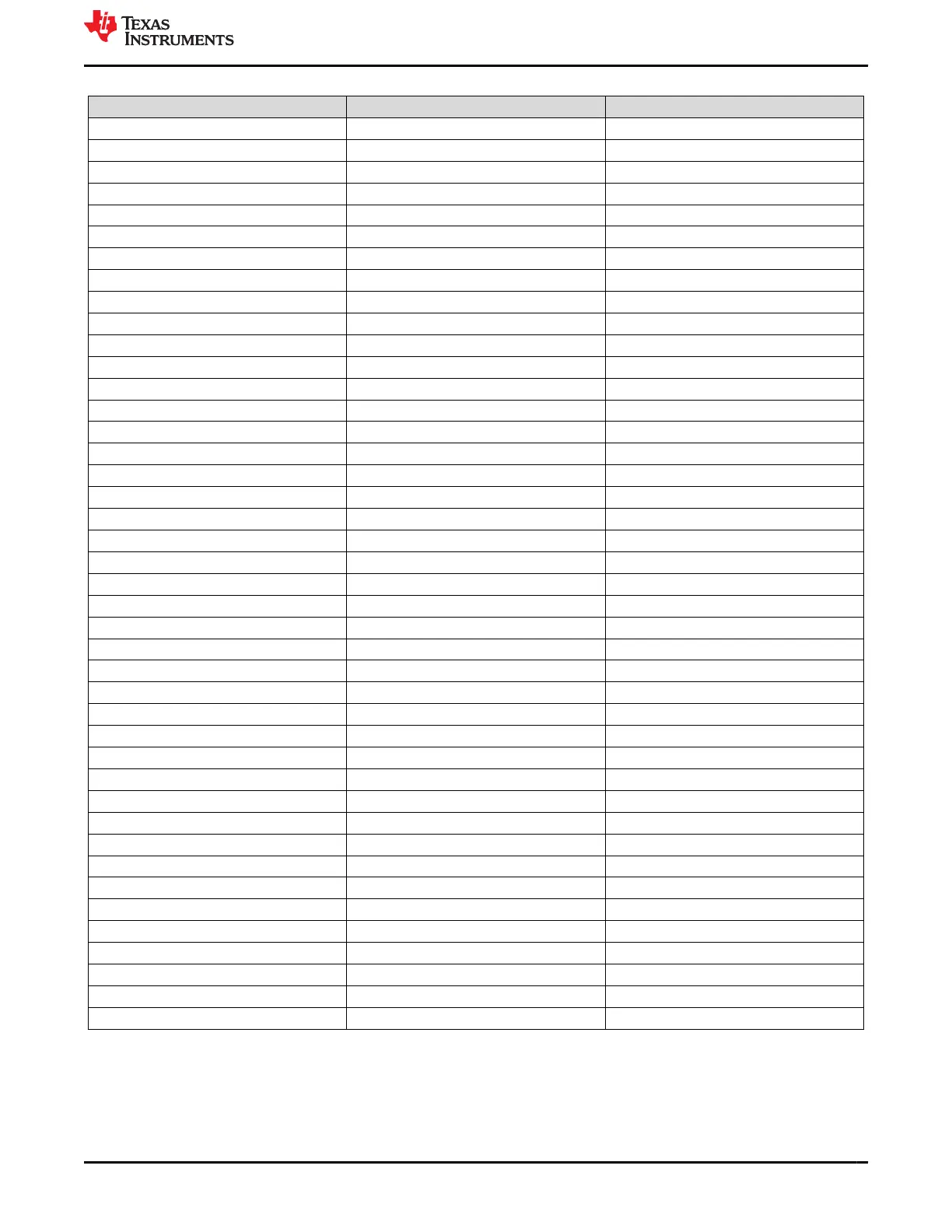

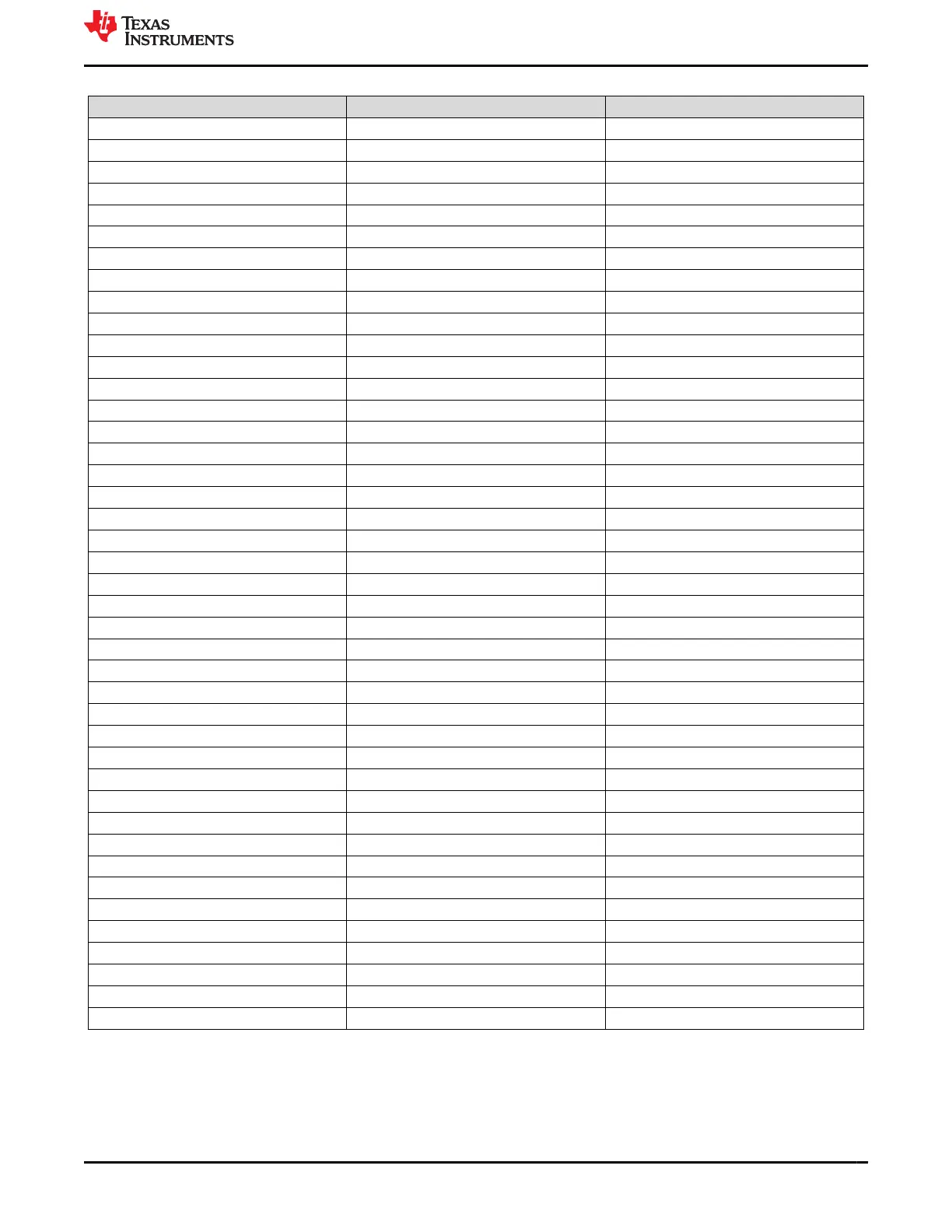

Table 3-17. Test Automation Header (J38) Pin-out

Pin No. Signal IO Direction (to CP board)

1 VCC3V3_1 Power (out)

2 VCC3V3_1 Power (out)

3 VCC3V3_1 Power (out)

4 NC NA

5 NC NA

6 NC NA

7 DGND Ground

8 NC NA

9 NC NA

10 NC NA

11 NC NA

12 NC NA

13 NC NA

14 NC NA

15 NC NA

16 DGND Ground

17 NC NA

18 NC NA

19 NC NA

20 NC NA

21 NC NA

22 NC NA

23 NC NA

24 NC NA

25 DGND Ground

26 TEST_POWERDOWN Input

27 TEST_PORz Input

28 TEST_WARMRESETn Input

29 NC NA

30 TEST_GPIO1 Bidirectional

31 TEST_GPIO2 Bidirectional

32 TEST_GPIO3 Input

33 TEST_GPIO4 Input

34 DGND Ground

35 NC NA

36 SOC_I2C1_SCL Bidirectional

37 BOOTMODE_I2C_SCL Bidirectional

38 SOC_I2C1_SDA Bidirectional

39 BOOTMODE_I2C_SDA Bidirectional

40 DGND Ground

41 DGND Ground

42 DGND Ground

www.ti.com System Description

SPRUIX0C – FEBRUARY 2021 – REVISED JUNE 2021

Submit Document Feedback

AM64x/AM243x GP EVM User's Guide 27

Copyright © 2021 Texas Instruments Incorporated

Loading...

Loading...