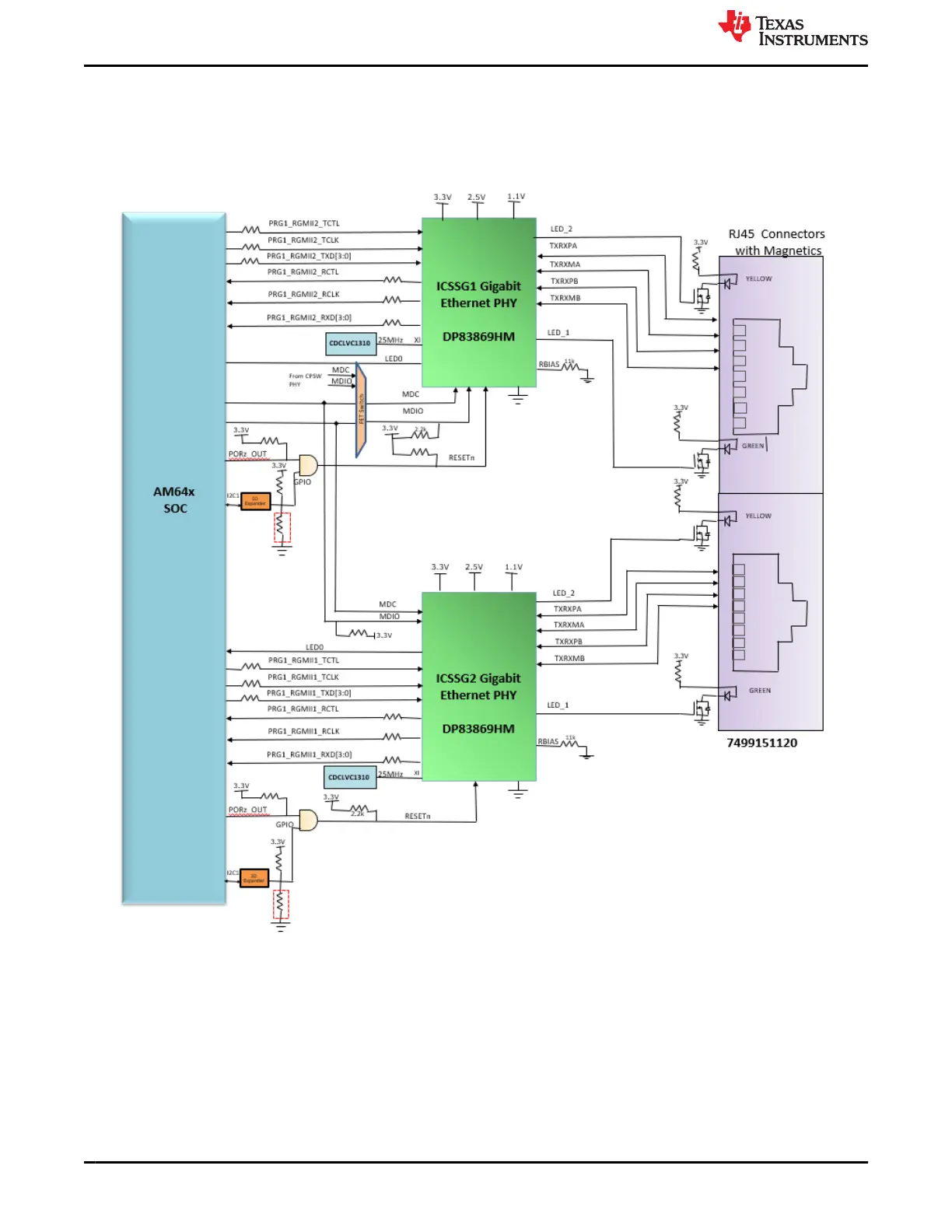

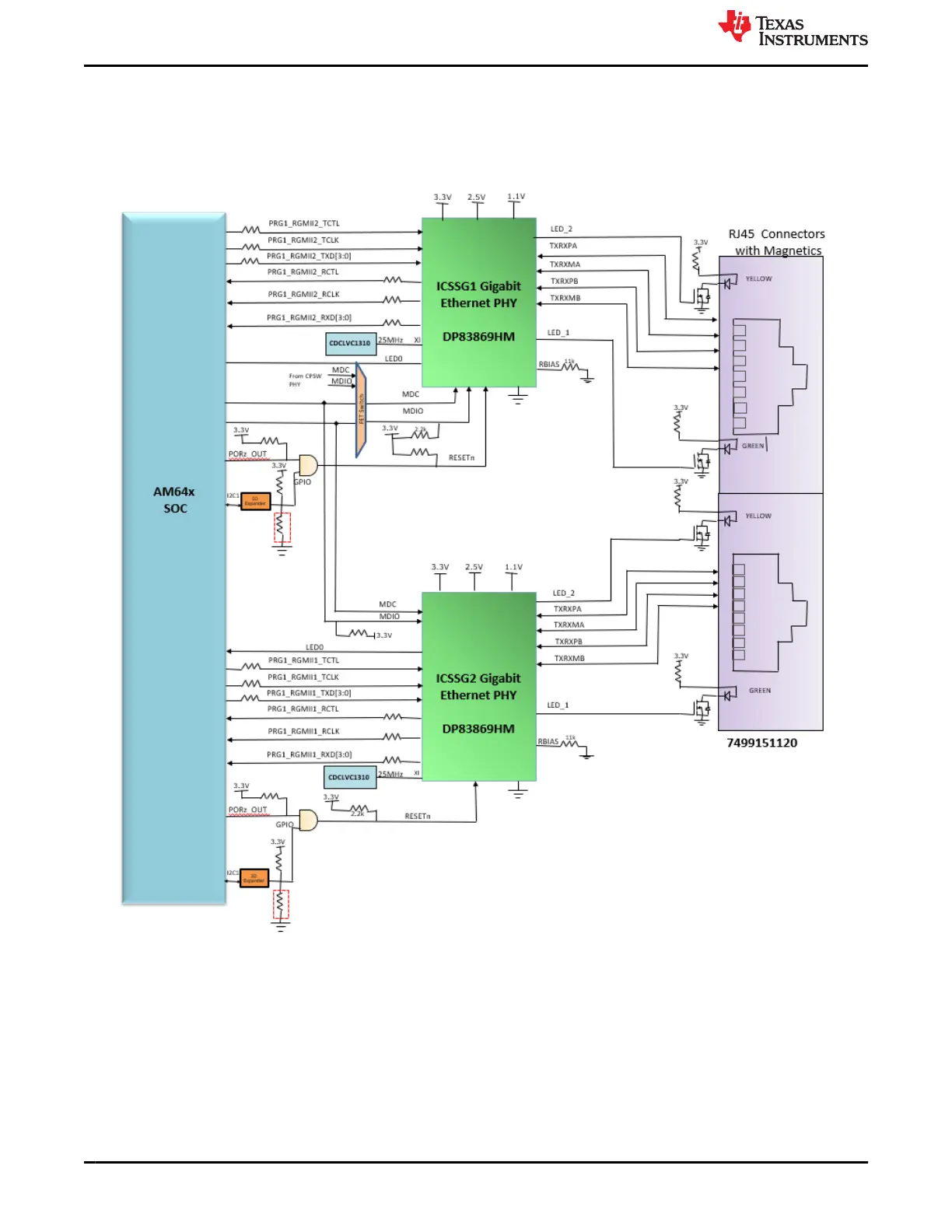

The third PHY (connected to stacked RJ45 connector J21A ) is interfaced to the PRG1_RGMII1 port of the

SoC. ICSSG ports support internal multiplexing of GPI, GPO, RGMII, MII etc. The objective of this PHY used to

connect to this port is that it should support both RGMII and MII modes (without the use of CRS and COL signals

as they are multiplexed with the CPSW_RGMII1 used for the first PHY). Hence the same DP83869 (48pin) PHY

is used for this port as well.

Figure 3-19. Ethernet Interface - ICSSG Domain

System Description

www.ti.com

34 AM64x/AM243x GP EVM User's Guide SPRUIX0C – FEBRUARY 2021 – REVISED JUNE 2021

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Loading...

Loading...