72

Analog Front End IC TMS37122 - Reference Guide August ’01

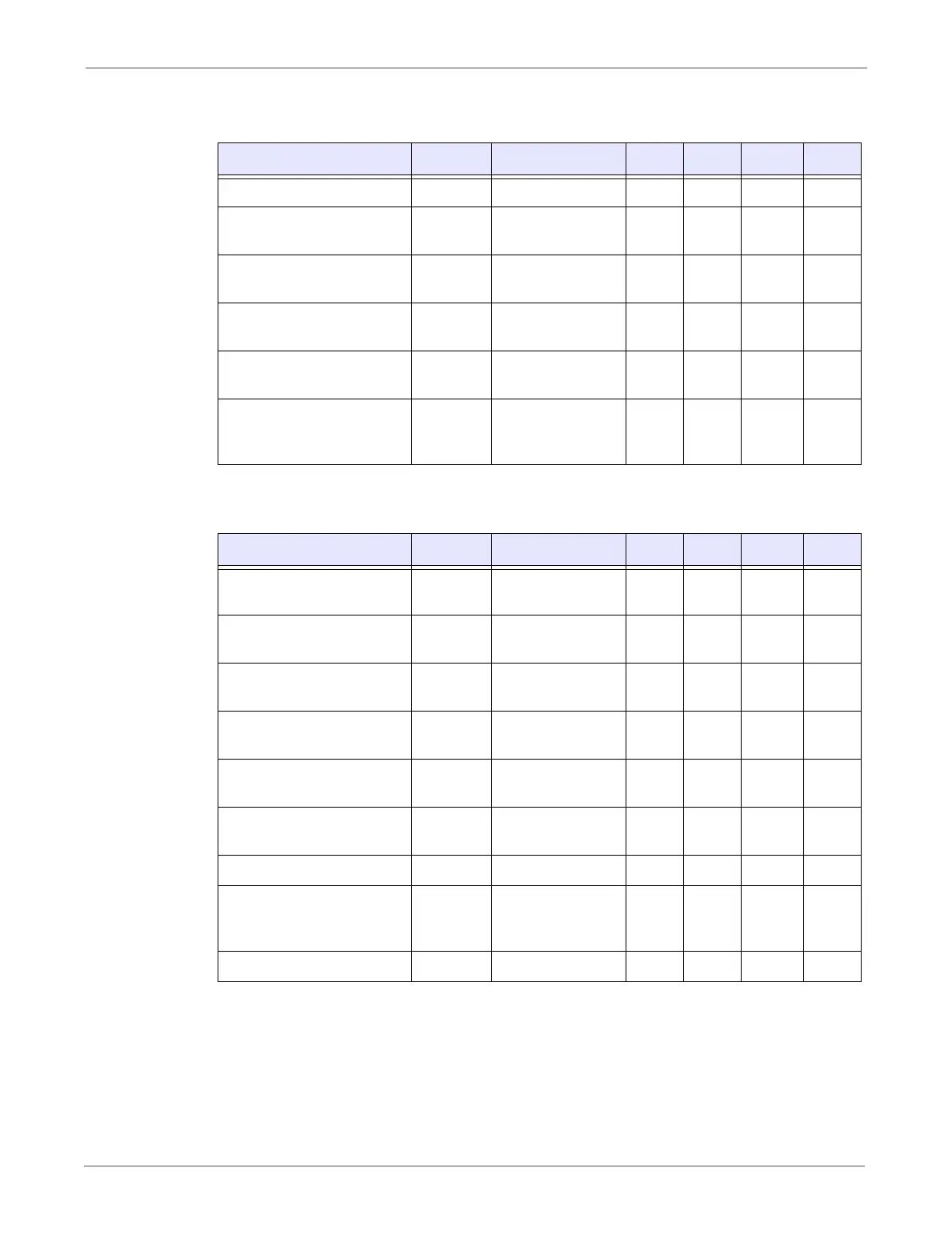

4.2.4.16 Control Interface

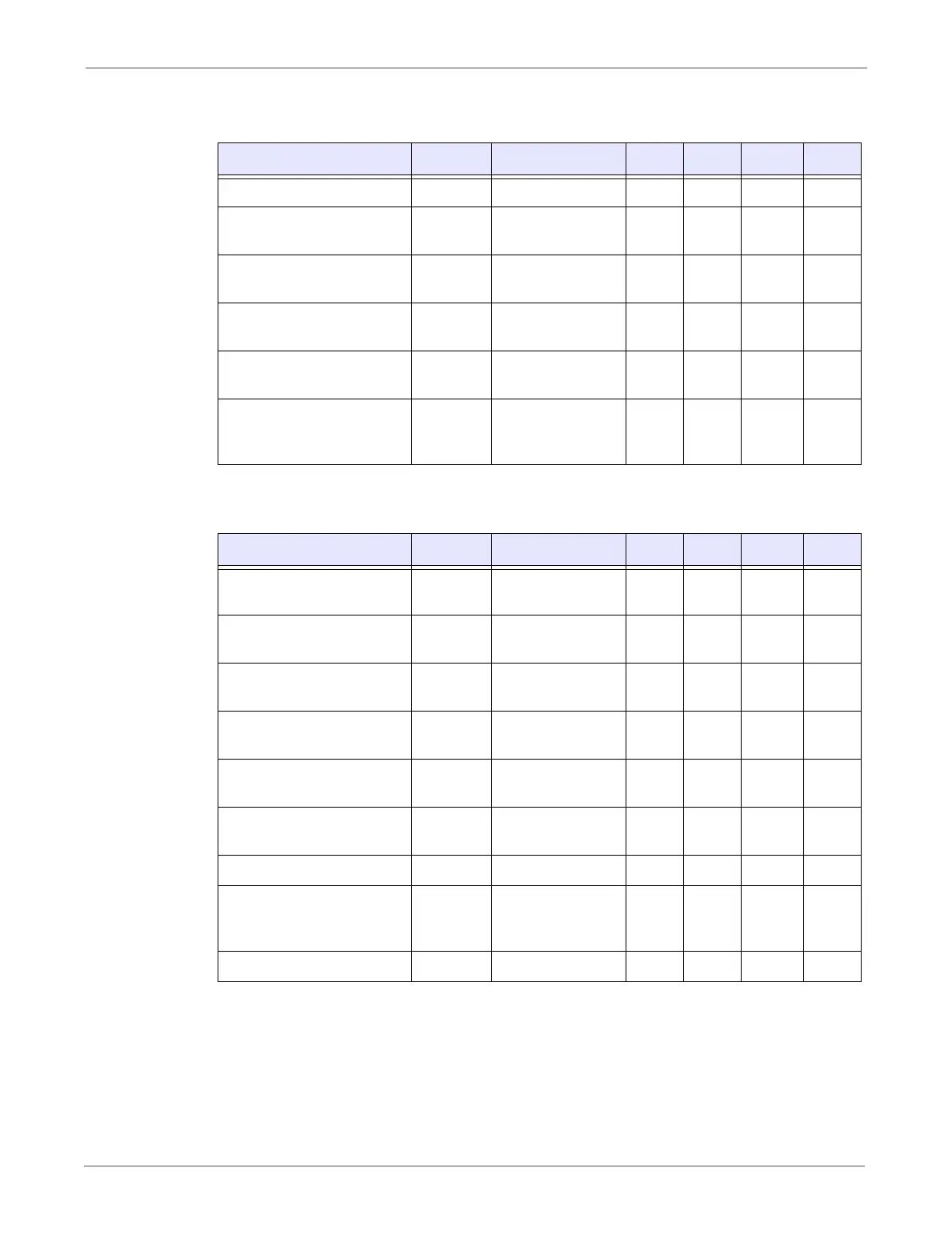

4.2.4.17 Clock Supervision

Parameter Sign Note Min Nom Max Unit

Input capacitance Ci WDEEN, MOD, TX 10 pF

Low Level Input Current IIL

VIL = 0 V,

VBAT = 4 V

-10 nA

High Level Input Current IIH

VIH = 4 V,

VBAT = 4 V

+10 nF

Low Level Output Voltage VOL

VBAT = 2 … 4 V,

RL = 100 kΩ

0.05 x

VBAT

0.07x

VBAT

V

High Level Output Voltage VOH

VBAT = 2 …4 V

RL = 100 kΩ

0.93 x

VBAT

0.95 x

VBAT

V

Rise and fall time tf

CL = 10 pF,

RL = 100 kΩ

VBAT = 2 …4 V

500 ns

Parameter Sign Note Min Nom Max Unit

Control Counter Clock

Frequency

fctrl fRES Hz

Wake Pattern Waiting Count

(configurable)

cwait 1024 16384

Wake Pattern Waiting Time

(configurable)

twait

fRES = 134.2 kHz,

twait = cwait/fRES

7.6 122.1 ms

Wake Pattern Waiting Count

Resolution

4bit

Wake Pattern Receive Time

(fix value)

twrx fRES = 134.2 kHz 15.3 ms

Wake Pattern Receive

Count (fix value)

cwrx 2048

Telegram Count ctelegr 4096 65536

Telegram Time ttelegr

fRES = 134.2 kHz,

ttelegr = ctelegr /

fRES

30.5 488.3 ms

Telegram Count Resolution 4 bit

Loading...

Loading...