ML605 Hardware User Guide www.xilinx.com 73

UG534 (v1.9) February 26, 2019

Detailed Description

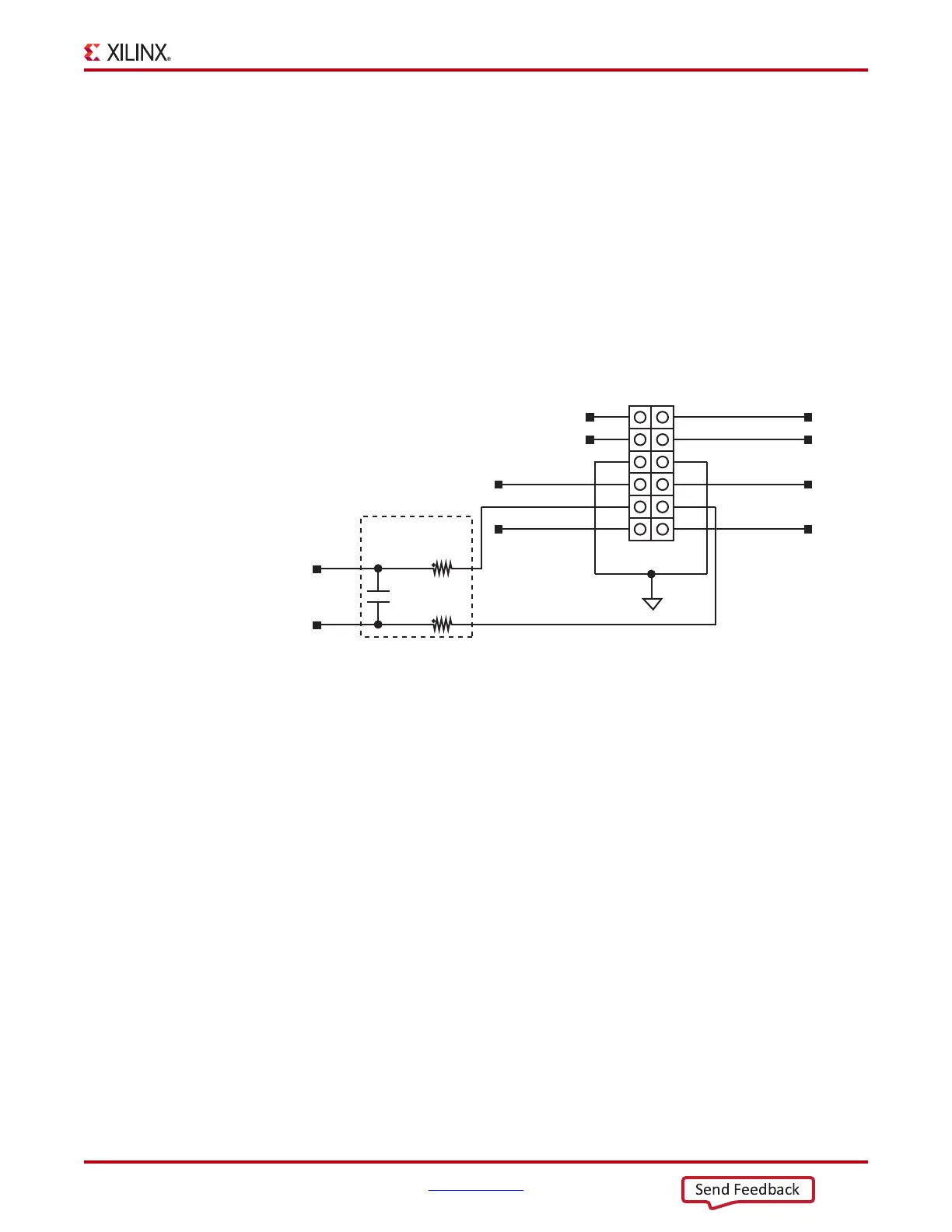

System Monitor Header (J35)

Figure 1-30 shows the pinout for the System Monitor 12-pin header. The header provides

user access to the analog power supply (A

Vdd

) and the 1.25V reference shown in

Figure 1-29. Access to the FPGA thermal diode and dedicated analog input channel

(Vp/Vn) is also provided on this header. The header can be used to connect user specific

analog signals and sensors to the system monitor.

The Kelvin points for a 5 mΩ current sensing shunt in the FPGA 1V V

ccint

core supply are

also available on this header. By connecting header pins 9 to 11 and 10 to 12 using jumpers,

the system monitor can be used to monitor the FPGA core current and power

consumption. This can be used to collect useful power information about a particular

design or implementation.

X-Ref Target - Figure 1-3 0

Figure 1-30: System Monitor Header (J35)

System Monitor

Header

Dedicated Analog Inputs

FPGA

Thermal Diode

access

To Measure VCCINT Current:

Jumper on 9-11, 10-12

Connect Vccint shunt to Vp,Vn

Vccint_shunt_N

Vccint_shunt_P

C169

0.01UF

16V

X7R

FPGA_DX_N

FPGA_DX_P

NC

NC

SYSMON_AVDD

1.25V Reference

12

3

56

78

910

4

1211

J35

SYSMON_VP

SYSMON_VN

R232

100

1/16W

1%1%

1/16W

100

R233

AGND

Anti-alias Filter

UG534_37 _081209

Loading...

Loading...