Platform Cable USB II

DS593 (v1.2.1) March 17, 2011 www.xilinx.com

27

Signal Integrity

Platform Cable USB II uses high-slew-rate buffers to drive its output pins. Each buffer has a 30.1Ω series termination

resistor. Users should pay close attention to PCB layout to avoid transmission line effects. Visit the Xilinx Signal Integrity

Central website, and see XAPP361, Planning for High Speed XC9500XV Designs for detailed signal integrity assistance.

If the target system has only one programmable device, the 2-mm connector should be located as close as possible to the

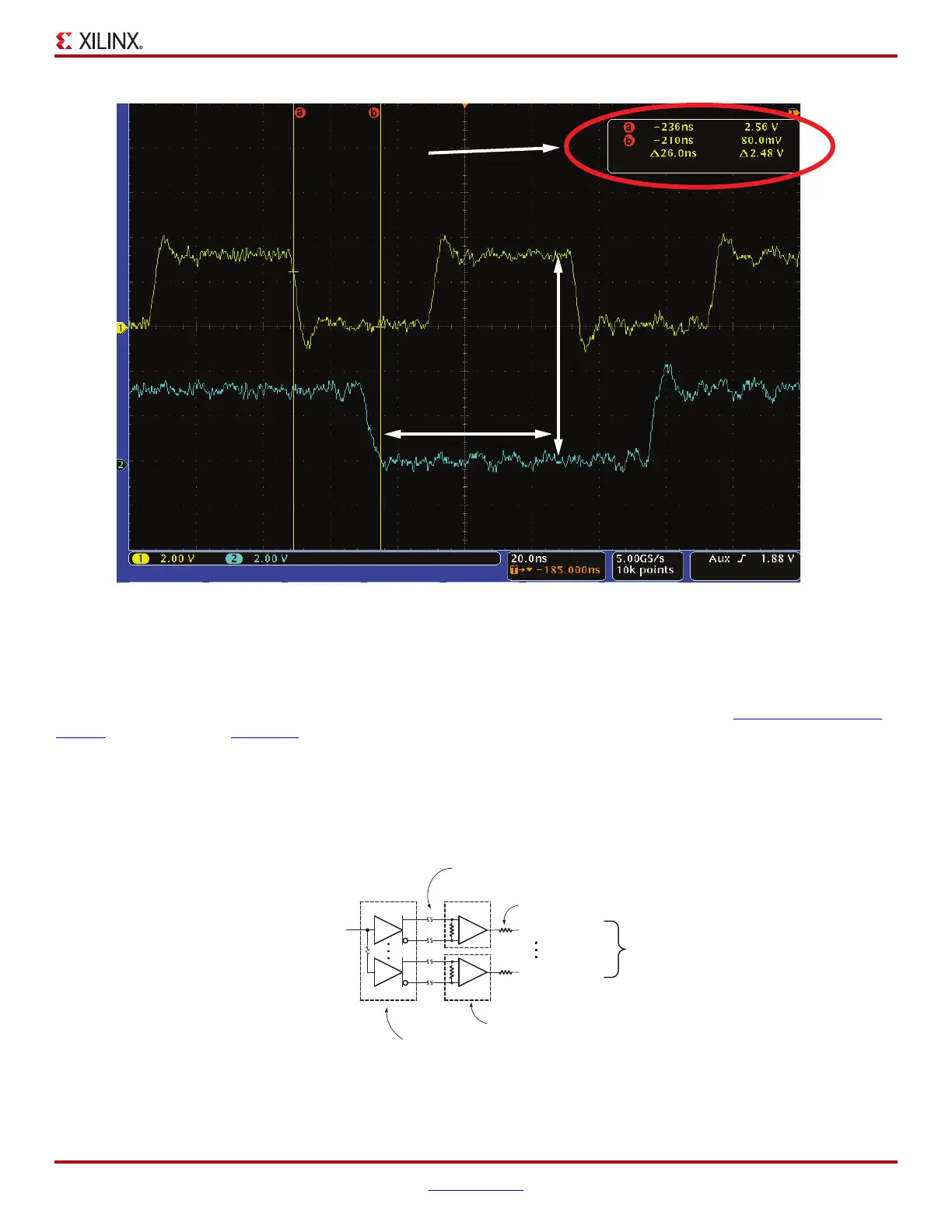

target device. If there are multiple devices in a JTAG or slave-serial single chain on the target system, users should consider

buffering TCK_CCLK_SCK. Differential driver/receiver pairs provide excellent signal quality when the rules identified in

Figure 29 are followed. Buffering is essential if target devices are distributed over a large PCB area.

Each differential driver and/or receiver pair contributes approximately 5 ns of propagation delay. This delay is insignificant

when using 12 MHz or slower clock speeds.

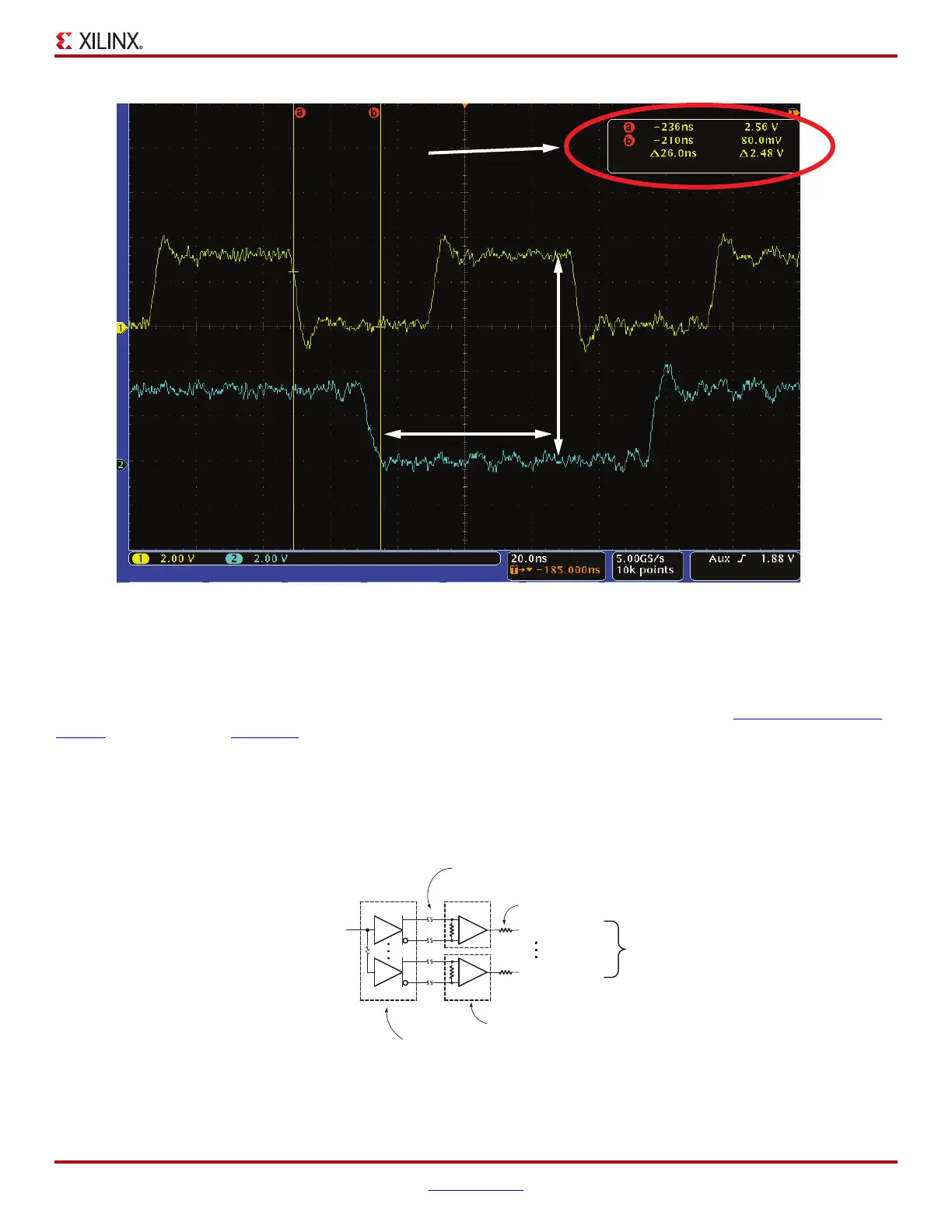

X-Ref Target - Figure 28

Figure 28: TDO Sampling Example at 12 MHz (Analog Signals on Target System)

X-Ref Target - Figure 29

Figure 29: Differential Clock Buffer Example

DS593_28_021408

Propagation delay from A to B (26 ns) captured directly at

the target represents 70% of the total propagation delay

seen by the cable (Figure 25).

TCK

TDO

TDO Sampling Point

TDO Sampling Point

SN65LVDS105

Four Differential

Drivers

SN65LVDS2 (2)

TCK_CCLK_SCK

TCK_CCLK_SCK1

1

4

TCK_CCLK_SCK4

DS593_29_021408

Locate driver package adjacent to 2-mm connector

Route A & B traces for each differential

pair in parallel with equal length and

consistent spacing

Locate one receiver adacent

to each target device

Four

Buffered

Clocks

Series Termination Resistor

(20Ω −30Ω)

Loading...

Loading...