Zynq UltraScale+ VCU TRD User Guide 63

UG1250 (v2019.1) May 29, 2019 www.xilinx.com

Chapter 5: Hardware Platform

the Zynq® UltraScale+ MPSoC PS DDR memory. The Video Frame Buffer IP can write a

variety of video formats to the Zynq UltraScale+ MPSoC PS DDR memory.

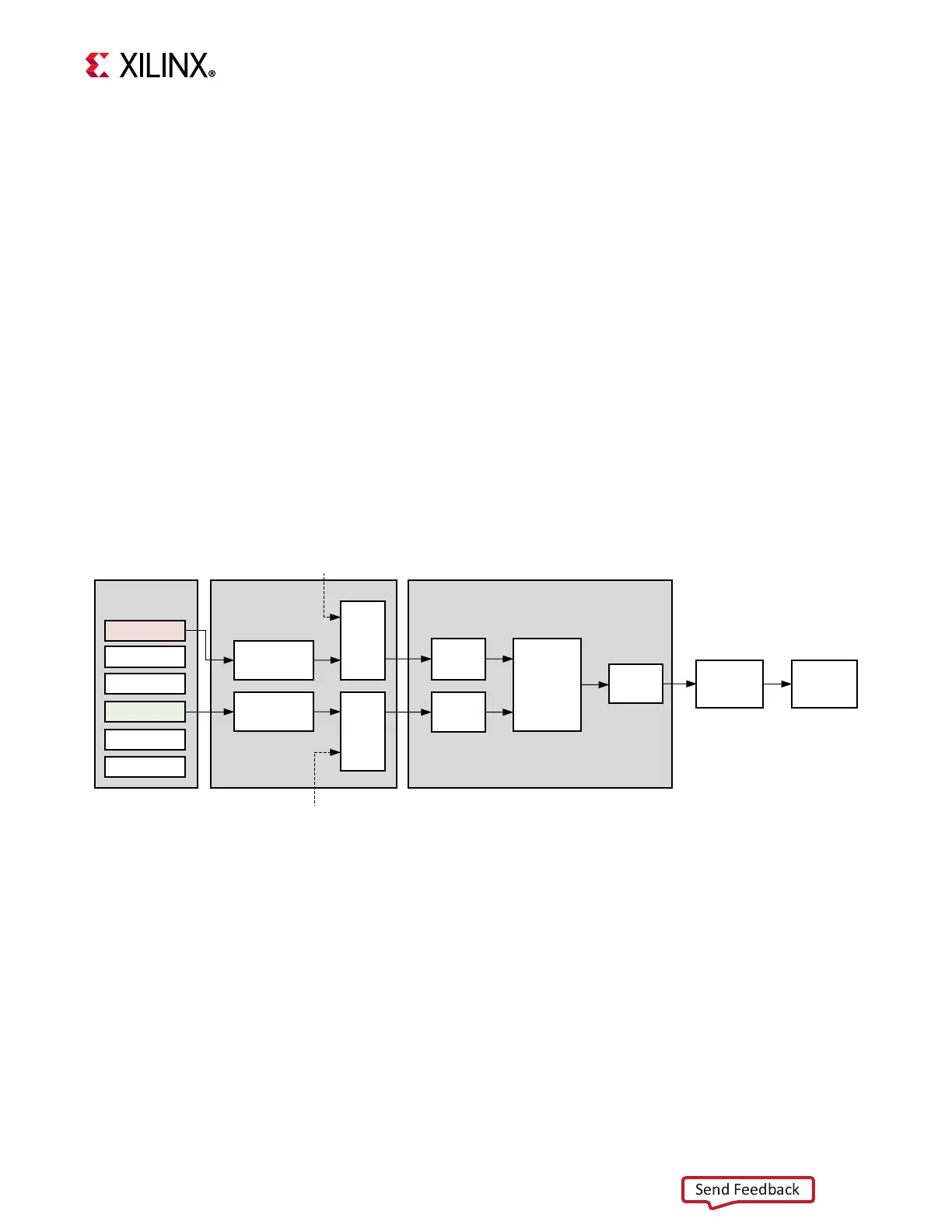

DP TX Display Pipeline

The DP TX display pipeline (see Figure 5-7) is configured to read video frames from

memory via two separate channels: one for video, the other for graphics. The video and

graphics layers are alpha-blended to create a single output video stream that is sent to the

monitor via the DisplayPort controller. This design does not use the audio feature of the

DisplayPort controller, therefore it is not discussed in this user guide. The major

components used in this design, as shown in the figure, are:

• DisplayPort DMA (DPDMA)

• Audio/Video (A/V) buffer manager

• Video blender

• DisplayPort controller (DP TX)

• PS-GTR gigabit transceivers

The DPDMA is a 6-channel DMA engine that fetches data from memory and forwards it to

the A/V buffer manager. The video layer can consist of up to three channels, depending on

the chosen pixel format, whereas the graphics layer is always a single channel. The used

pixel formats are described in Video Buffer Format. The remaining two channels are used

for audio.

The A/V buffer manager can receive data either from the DPDMA (non-live mode) or from

the PL (live mode) or a combination of the two. In this design, only non-live mode is used

for both video and graphics. The three video channels feed into a video pixel unpacker and

the graphics channel into a graphics pixel unpacker. Because the data is not timed in

non-live mode, video timing is locally generated using the internal Video Timing Controller.

X-Ref Target - Figure 5-7

Figure 5-7: Display Pipeline Showing DPDMA, A/V Buffer Manager, Video Blender, and DP Transmitter

DP Tx

BlenderA/V Buffer

Manager

DPDMA

Vid Ch 0

Vid

Unpacker

Gfx

Unpacker

Vid

Mux

Gfx

Mux

CRS/

CSC

CRS/

CSC

Alpha

Blender

CRS/

CSC

Live from PL

Live from PL

PS-GTR

Vid Ch 1

Vid Ch 2

Gfx Ch 0

Aud Ch 0

Aud Ch 1

X20151-112718

Loading...

Loading...