Zynq UltraScale+ VCU TRD User Guide 68

UG1250 (v2019.1) May 29, 2019 www.xilinx.com

Chapter 5: Hardware Platform

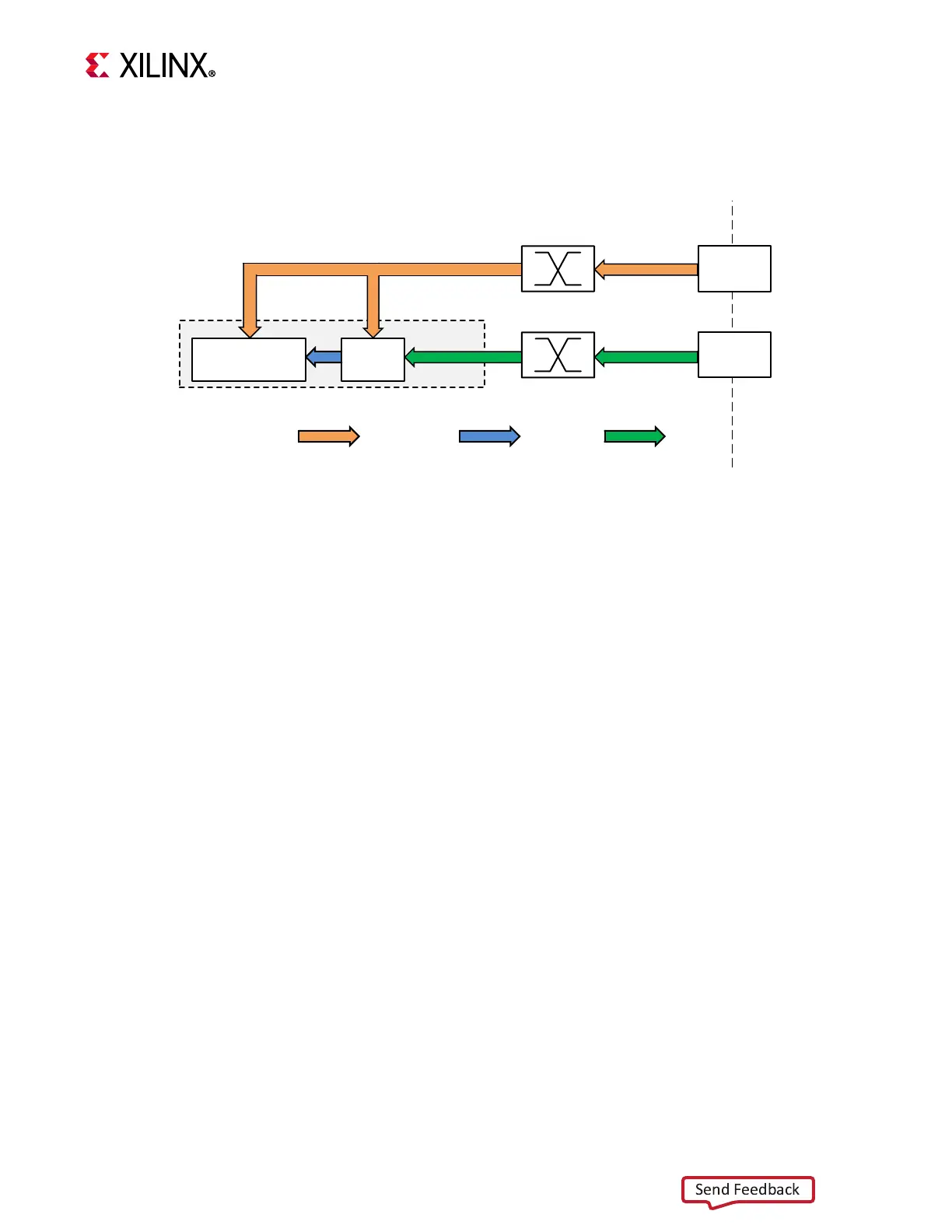

Ethernet 10G Output Pipeline

The Ethernet 10G output pipeline is shown in Figure 5-11.

This pipeline consists of two main components—the 10G/25G high speed Ethernet

Subsystem and AXI DMA, each shared with the Ethernet 10G input/capture pipeline. Refer

to Ethernet 10G Input/Capture Pipeline for more information and for the configuration of

each component.

X-Ref Target - Figure 5-11

Figure 5-11: Ethernet 10G Output Pipeline

Ethernet 10G/25G

Subsystem

AXI

DMA

HPM0/1

HP0

PL

AXI-Lite AXI-Stream AXI-MM

128

128

32

6464

Ethernet 10G Output/Capture Pipeline

PS

X21947-120318X21947-042419

Loading...

Loading...