Zynq UltraScale+ VCU TRD User Guide 69

UG1250 (v2019.1) May 29, 2019 www.xilinx.com

Chapter 5: Hardware Platform

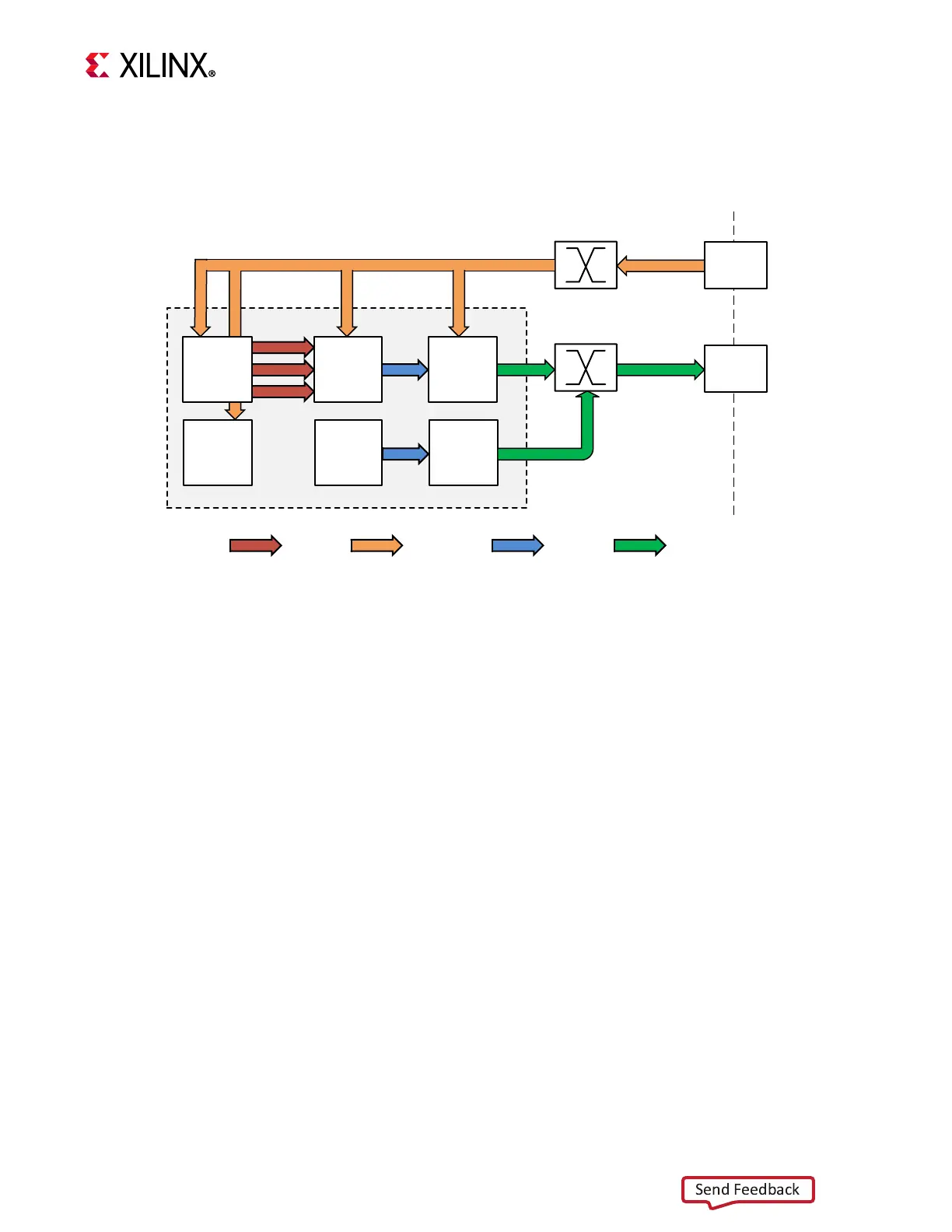

HDMI Audio RX Pipeline

The HDMI audio RX pipeline is shown in Figure 5-12.

This pipeline consists of two components, each of them controlled by the APU through an

AXI4-Lite base register interface:

• The Video PHY Controller is shared with the HDMI RX and HDMI TX pipelines. Refer to

HDMI RX Capture Pipeline for more information on the VPHY and its configuration.

• The HDMI RX Subsystem is shared with the HDMI RX pipeline. Refer to HDMI RX

Capture Pipeline for more information on the VPHY and its configuration.

• The Audio Formatter provides high-bandwidth direct memory access between memory

and AXI4-Stream target peripherals. Initialization, status, and management registers are

accessed through an AXI4-Lite slave interface. It is configured with both read and write

interface enabled for a maximum of two audio channels and interleaved memory

packing mode with memory data format configured as AES to PCM.

Note:

The Audio Engineering Society (AES) standard was developed for the exchange of digital

audio signals between professional audio devices.

X-Ref Target - Figure 5-12

Figure 5-12: HDMI Audio RX Pipeline

HDMI RX

SS

HPM0/1

HP

PL

Rx Data AXI-Lite AXI-Stream AXI-MM

128

128 3232

HDMI Audio RX Pipeline

Audio

Formatter 1

32

40

40

40

PS

MIPI to

RX SS

I2S RX

SS

Audio

Formatter 2

32

Video

PHY

32

X21948-112718X21948-042619

Loading...

Loading...