MIL-STD-1553 Reference Manual

Chapter 7 – Bus Controller Functions

A

A

i

i

U

U

I

I

n

n

t

t

3

3

2

2

p

p

a

a

r

r

1

1

/

/

p

p

a

a

r

r

2

2

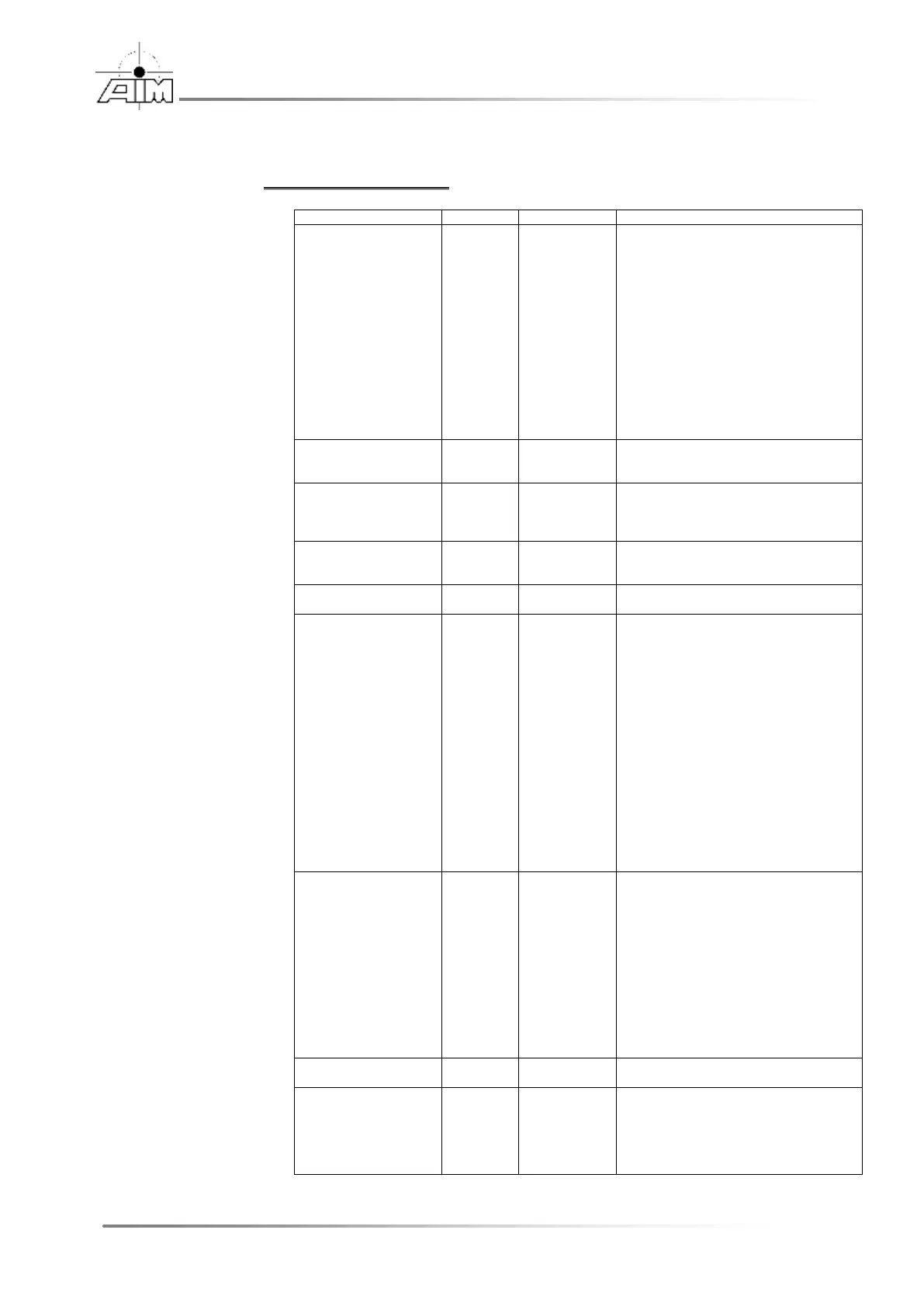

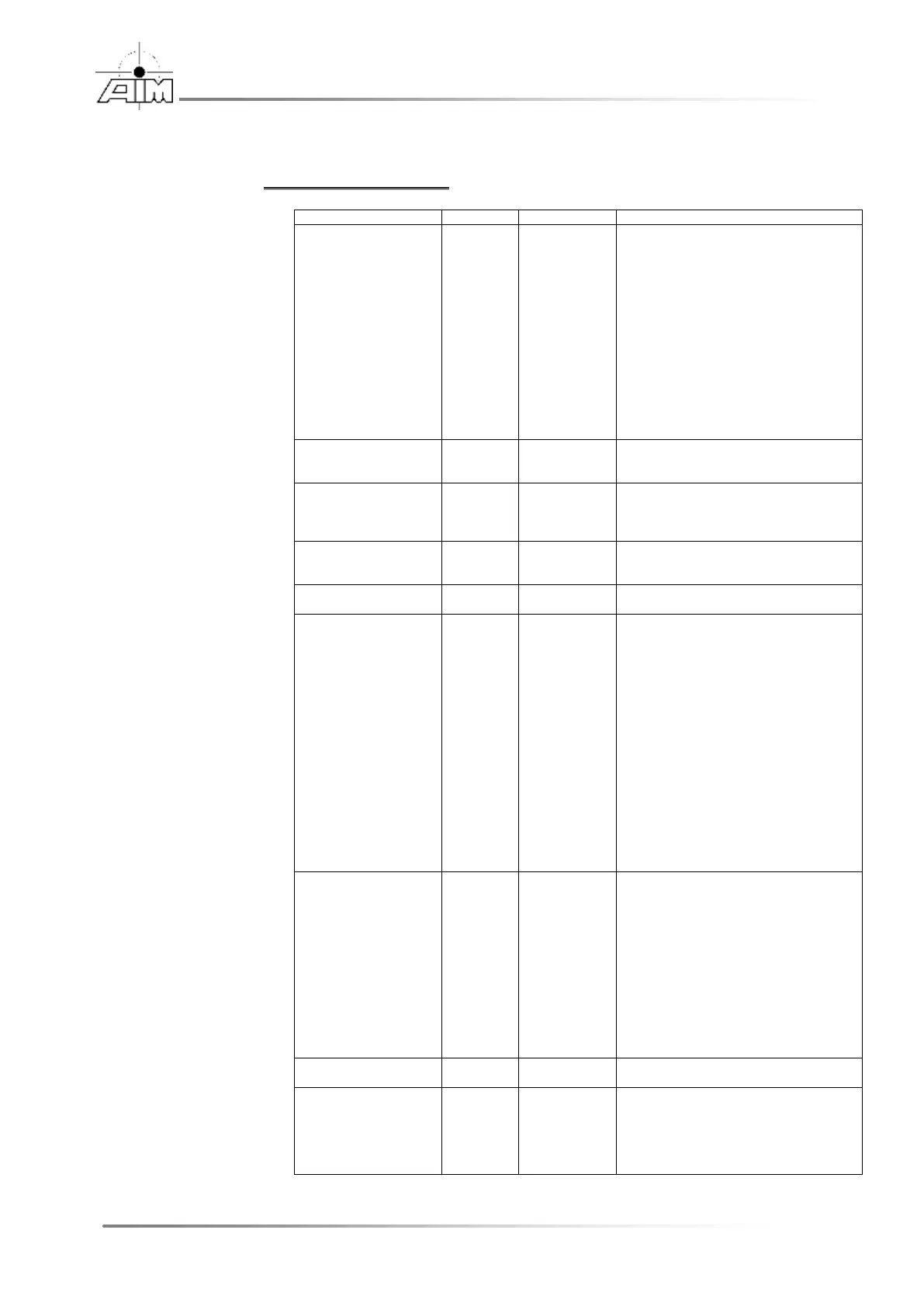

Instruction parameters

Execute BC Transfer identified by BC

Transfer ID <xid> (refer to function

ApiCmdBCXferDef)

For HS RT-RT type transfers two

contiguous entries are required within the

BC Intruction Table (corresponds to first

and second LS Action Word transfer). In

this case hs_xf_type shall be set to one of

the following values for the second entry:

API_HS_BC_TYPE_RTRT

API_HS_BC_TYPE_RTBR

APIEF_BC_TYPE_EERTRT

APIEF_BC_TYPE_E_RTBR

APIEF_BC_TYPE_E_RTBRMIXED

Execute pure EFEX BC Transfer identified

by HS BC Transfer ID <xid> (refer to

function Api3910CmdEfBCXferDef)

Call subtable / jump to Instruction Table

entry which is identified by <label>.

Subtable must be terminated with Return

opcode.

Return from subtable, execution of

instructions is continued with instruction

which is following the related Call opcode.

Absolute Jump to Instruction Table entry

which is identified by <label>.

Relative branch

Par1 / Bit 15-0 (OFFSET):

Number of instructions which shall be

skipped including current instruction

Par2 / Bit 0 (DIR) :

0 = branch forward

1 = branch backward

Par2 / Bit 1 (INT) :

0 = no interrupt

1 = assert interrupt on instruction

execution

All other bits are reserved

Note: A ‘No Operation’ instruction (NOP)

with interrupt can be implemented with

OFFSET=1, DIR=0, INT=1

Wait for external BC Trigger input

Par2 / Bit 0 (RES) :

reserved bit

Par2 / Bit 1 (SYN) :

0 = BC Minor Framing is not synchronized

1 = BC Minor Framing is synchronized to

external

trigger, such that all Minor Frames after

the trigger

are equally spaced

All other bits are reserved

Strobe external BC Trigger output

Decrement and Jump on zero, if Major

Frame Counter (MFC register in

Firmware) is not zero then instruction

execution continues with the following

instruction, if zero then jump to Instruction

Table entry which is identified by <label>.

Loading...

Loading...