UG-1098 ADE9000 Technical Reference Manual

Rev. 0 | Page 68 of 86

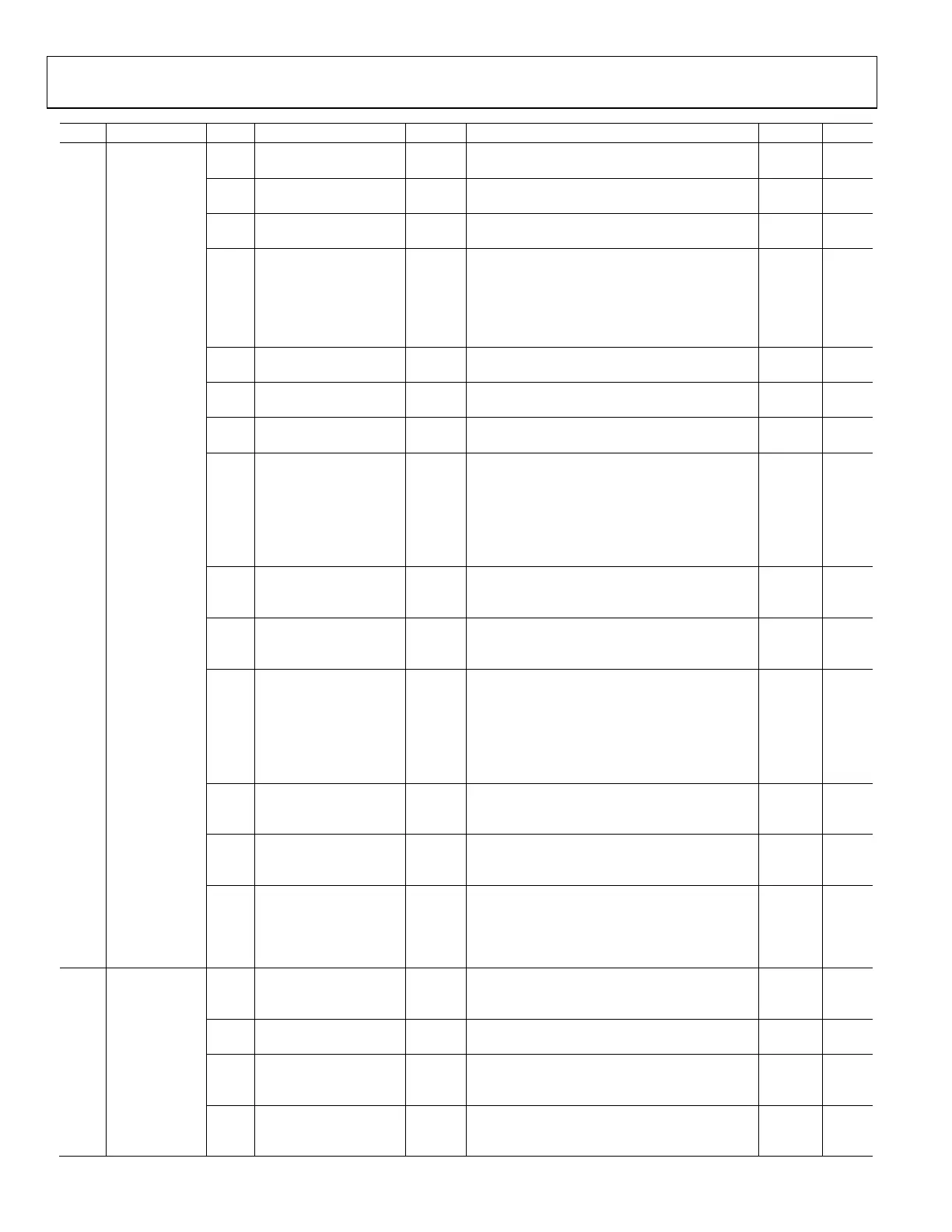

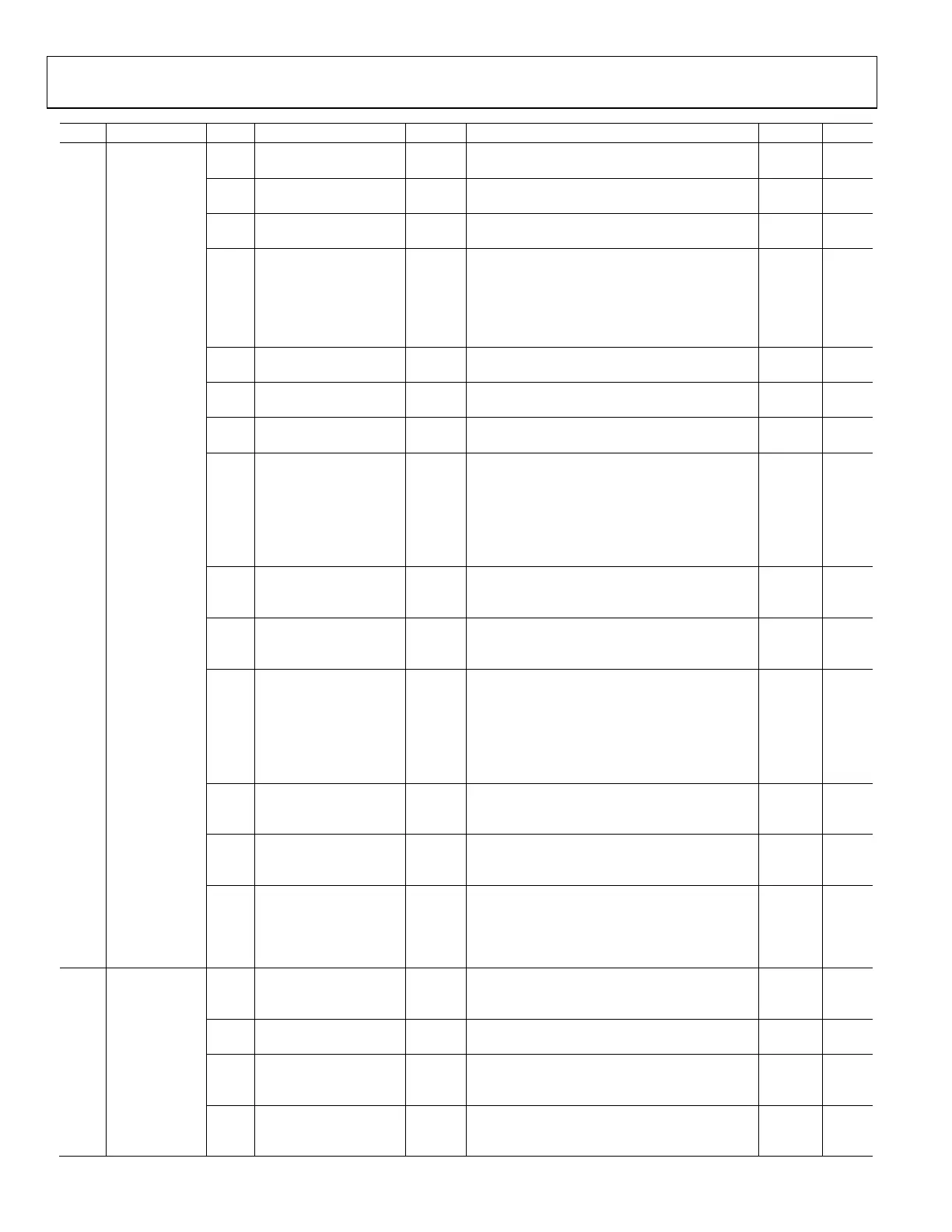

Addr. Name Bits Bit Name Settings Description Reset Access

This bit is set when a CF3 pulse is issued, when

the CF3 pin goes from a high to low state.

12 CF2 This bit is set when a CF2 pulse is issued, when

the CF2 pin goes from a high to low state.

0x0 R/W1

11 CF1 This bit is set when a CF1 pulse is issued, when

the CF1 pin goes from a high to low state.

0x0 R/W1

10 REVPSUM4 This bit is set to indicate if the CF4 polarity

changed sign. For example, if the last CF4 pulse

was positive reactive energy and the next CF4

pulse is negative reactive energy, the REVPSUM4

bit is set. This bit is updated when a CF4 pulse is

output, when the CF4 pin goes from high to low.

0x0 R/W1

9 REVPSUM3 This bit is set to indicate if the CF3 polarity

changed sign. See REVPSUM4.

0x0 R/W1

8 REVPSUM2 This bit is set to indicate if the CF2 polarity

changed sign. See REVPSUM4.

0x0 R/W1

7 REVPSUM1 This bit is set to indicate if the CF1 polarity

changed sign. See REVPSUM4.

0x0 R/W1

6 REVRPC This bit indicates if the Phase C total or

fundamental reactive power has changed sign.

The PWR_SIGN_SEL bit in the EP_CFG register

selects whether total or fundamental reactive

power is monitored. This bit is updated when the

power values in the xVAR_ACC and xFVAR_ACC

registers update, after PWR_TIME 8 kSPS samples.

0x0 R/W1

5 REVRPB This bit indicates if the Phase B total or

fundamental reactive power has changed sign.

See REVRPC.

0x0 R/W1

4 REVRPA This bit indicates if the Phase A total or

fundamental reactive power has changed sign.

See REVRPC.

0x0 R/W1

3 REVAPC This bit indicates if the Phase C total or

fundamental active power has changed sign.

The PWR_SIGN_SEL bit in the EP_CFG register

selects whether total or fundamental active power

is monitored. This bit is updated when the power

values in the xWATT_ACC and xFWATT_ACC

registers update, after PWR_TIME 8 kSPS samples.

0x0 R/W1

2 REVAPB This bit indicates if the Phase B total or

fundamental active power has changed sign.

See REVAPC.

0x0 R/W1

1 REVAPA This bit indicates if the Phase A total or

fundamental active power has changed sign.

See REVAPC.

0x0 R/W1

0 EGYRDY This bit is set when the power values in the

xWATTHR xVAHR, xVARHR, xFVARHR, xFWATTHR,

xFVAHR registers update, after EGY_TIME 8 kSPS

samples or line cycles, depending on the

EGY_TMR_MODE bit in the EP_CFG register.

0x0 R/W1

0x403 STATUS1 31 ERROR3 This bit indicates an error and generates a non-

maskable interrupt. Issue a software or hardware

reset to clear this error.

0x0 R/W1

30 ERROR2 This bit indicates that an error was detected and

corrected. No action is required.

0x0 R/W1

29 ERROR1 This bit indicates an error and generates a non-

maskable interrupt. Issue a software or hardware

reset to clear this error.

0x0 R

28 ERROR0 This bit indicates an error and generates a non-

maskable interrupt. Issue a software or hardware

reset to clear this error.

0x0 R

Loading...

Loading...