ADE9000 Technical Reference Manual UG-1098

Rev. 0 | Page 71 of 86

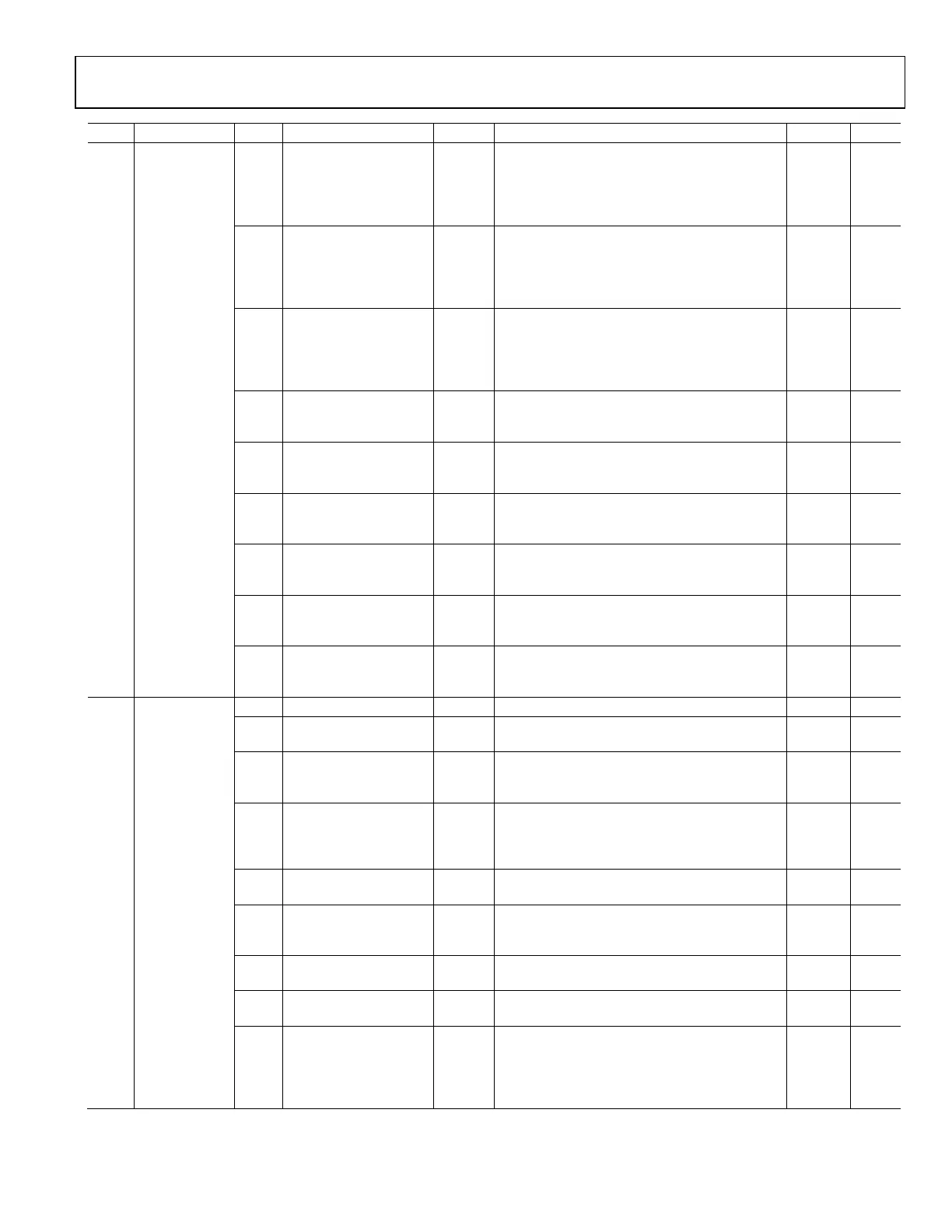

Addr. Name Bits Bit Name Settings Description Reset Access

This bit indicates the sign of the last CF3 pulse. A

zero indicates that the pulse was from negative

energy and a one indicates that the energy was

positive. This bit is updated when a CF3 pulse is

output, when the CF3 pin goes from high to low.

7 REVPSUM2

This bit indicates the sign of the last CF2 pulse. A

zero indicates that the pulse was from negative

energy and a one indicates that the energy was

positive. This bit is updated when a CF2 pulse is

output, when the CF2 pin goes from high to low.

0x0 R

6 REVPSUM1

This bit indicates the sign of the last CF1 pulse. A

zero indicates that the pulse was from negative

energy and a one indicates that the energy was

positive. This bit is updated when a CF1 pulse is

output, when the CF1 pin goes from high to low.

0x0 R

5 SWELLC This bit is equal to one when the Phase C

voltage is in the swell condition and is zero

when it is not in a swell condition.

0x0 R

4 SWELLB

This bit is equal to one when the Phase B voltage

is in the swell condition and is zero when it is not

in a swell condition.

0x0 R

This bit is equal to one when the Phase A

voltage is in the swell condition and is zero

when it is not in a swell condition.

2 DIPC This bit is equal to one when the Phase C

voltage is in the dip condition and is zero when

it is not in a dip condition.

0x0 R

1 DIPB

This bit is equal to one when the Phase B voltage

is in the dip condition and is zero when it is not

in a dip condition

0x0 R

0 DIPA This bit is equal to one when the Phase A

voltage is in the dip condition and is zero when

it is not in a dip condition.

0x0 R

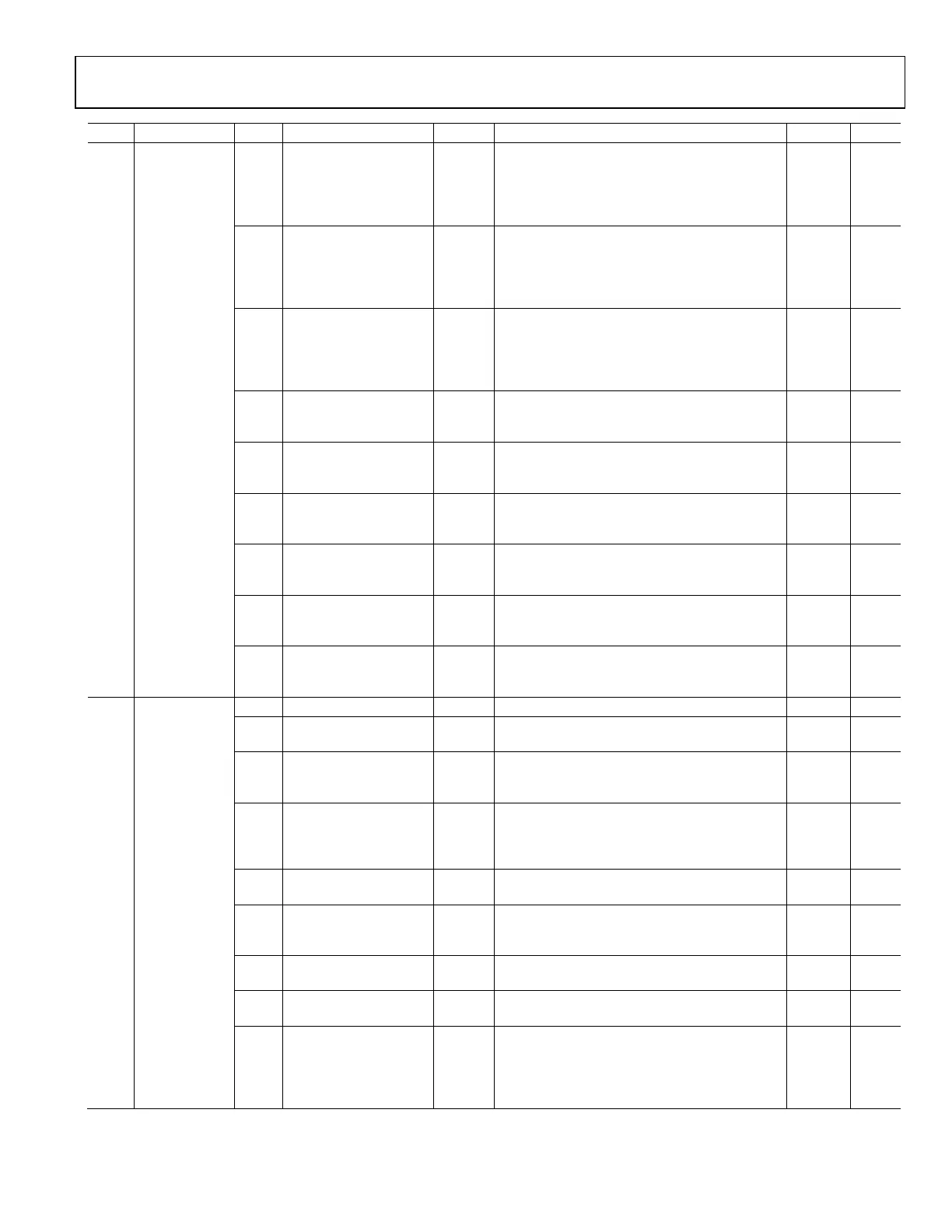

0x405 MASK0 [31:26] RESERVED Reserved. 0x0 R

25 TEMP_RDY_MASK Set this bit to enable an interrupt when a new

temperature measurement is available.

0x0 R/W

24 MISMTCH

Set this bit to enable an interrupt when there is a

change in the relationship between ISUMRMS

and ISUMLVL.

0x0 R/W

23 COH_WFB_FULL Set this bit to enable an interrupt when the

waveform buffer is full with resampled data,

which is selected when WF_CAP_SEL = 0 in the

WFB_CFG register.

0x0 R/W

22 WFB_TRIG Set this bit to enable an interrupt when one of

the events configured in WFB_TRIG_CFG occurs.

0x0 R/W

21 THD_PF_RDY Set this bit to enable an interrupt when the THD

and power factor measurements are updated,

every 1.024 sec.

0x0 R/W

20 RMS1012RDY Set this bit to enable an interrupt when the

10 cycle rms/12 cycle rms values are updated.

0x0 R/W

19 RMSONERDY Set this bit to enable an interrupt when the fast

RMS½ values are updated.

0x0 R/W

18 PWRRDY Set this bit to enable an interrupt when the

power values in the xWATT_ACC, xVA_ACC,

xVAR_ACC, xFWATT_ACC, xFVA_ACC, and

xFVAR_ACC registers update, after PWR_TIME

8 kSPS samples.

0x0 R/W

Loading...

Loading...