UG-1098 ADE9000 Technical Reference Manual

Rev. 0 | Page 72 of 86

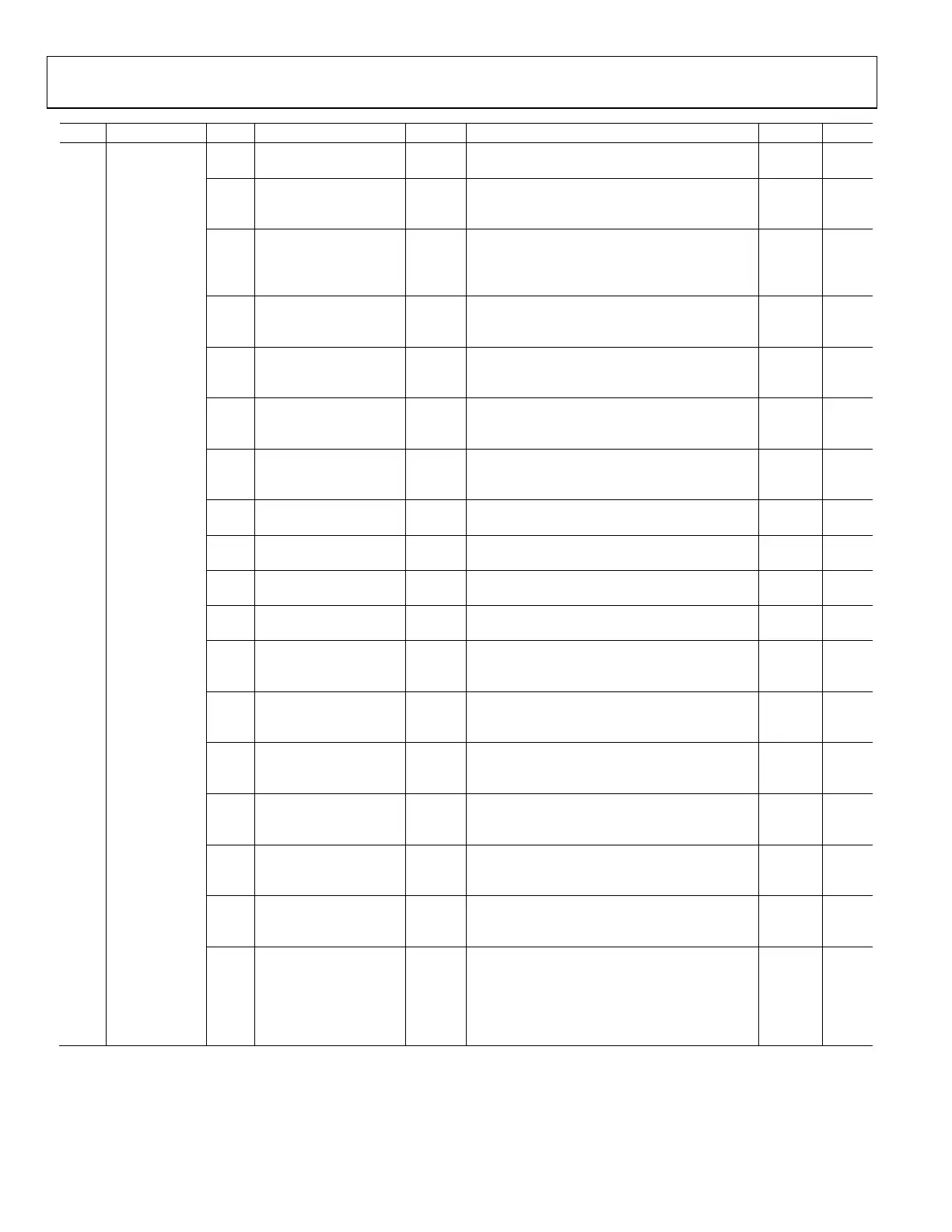

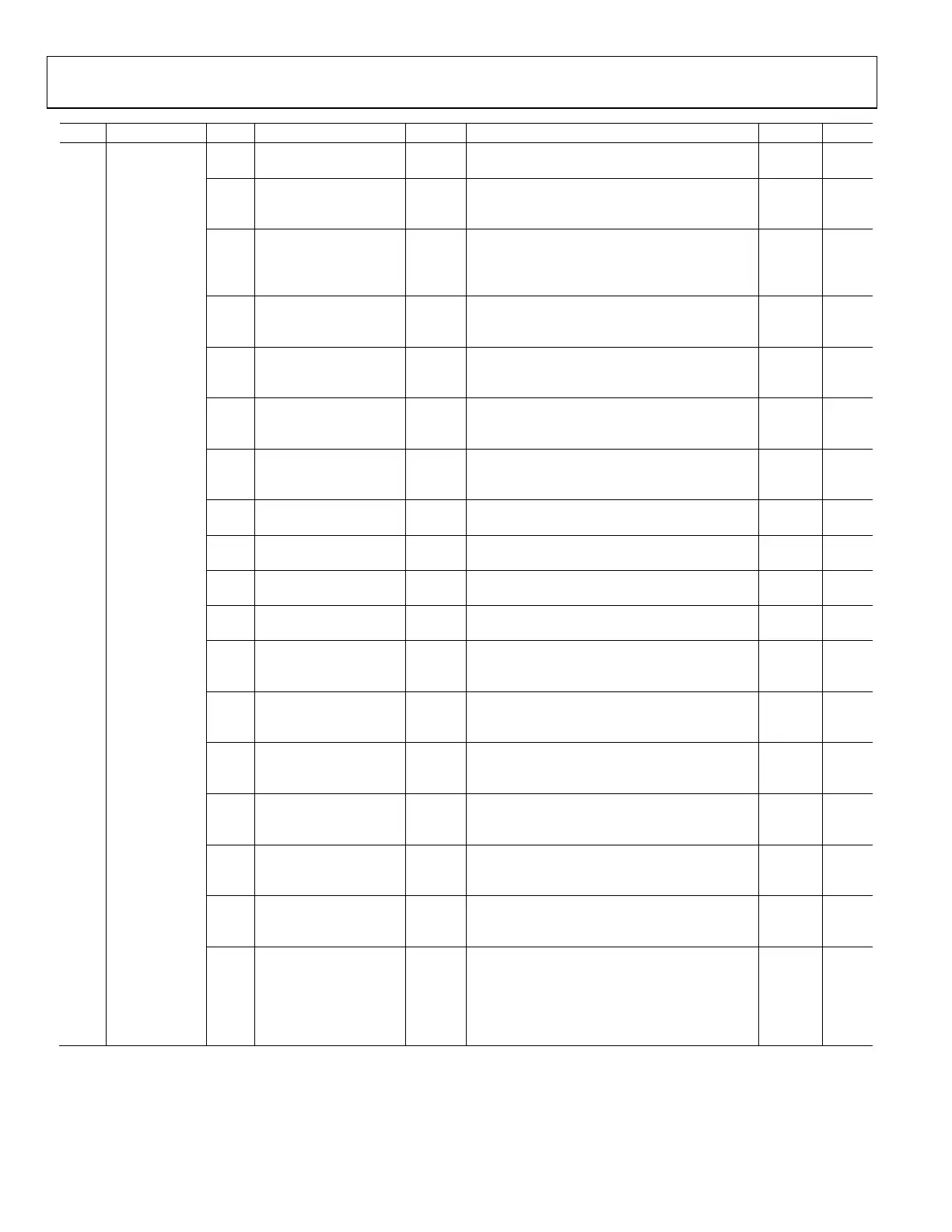

Addr. Name Bits Bit Name Settings Description Reset Access

Set this bit to enable an interrupt when a page

enabled in the WFB_PG_IRQEN register is filled.

16 WFB_TRIG_IRQ Set this bit to enable an interrupt when This bit

is set when the waveform buffer has stopped filling

after an event configured in WFB_TRIG_CFG occurs.

0x0 R/W

15 DREADY Set this bit to enable an interrupt when new

waveform samples are ready. The update rate

depends on the data selected in the WF_SRC bits in

the WFB_CFG register.

0x0 R/W

14 CF4 Set this bit to enable an interrupt when the CF4

pulse is issued, when the CF4 pin goes from a

high to low state.

0x0 R/W

13 CF3 Set this bit to enable an interrupt when the CF3

pulse is issued, when the CF3 pin goes from a

high to low state.

0x0 R/W

12 CF2 Set this bit to enable an interrupt when the CF2

pulse is issued, when the CF2 pin goes from a

high to low state.

0x0 R/W

11 CF1 Set this bit to enable an interrupt when the CF1

pulse is issued, when the CF1 pin goes from a

high to low state.

0x0 R/W

10 REVPSUM4 Set this bit to enable an interrupt when the CF4

polarity changed sign.

0x0 R/W

9 REVPSUM3 Set this bit to enable an interrupt when the CF3

polarity changed sign.

0x0 R/W

8 REVPSUM2 Set this bit to enable an interrupt when the CF2

polarity changed sign.

0x0 R/W

7 REVPSUM1 Set this bit to enable an interrupt when the CF1

polarity changed sign.

0x0 R/W

6 REVRPC Set this bit to enable an interrupt when the

Phase C total or fundamental reactive power has

changed sign.

0x0 R/W

5 REVRPB Set this bit to enable an interrupt when the

Phase C total or fundamental reactive power has

changed sign.

0x0 R/W

4 REVRPA Set this bit to enable an interrupt when the

Phase A total or fundamental reactive power has

changed sign.

0x0 R/W

3 REVAPC Set this bit to enable an interrupt when the

Phase C total or fundamental active power has

changed sign.

0x0 R/W

2 REVAPB Set this bit to enable an interrupt when the

Phase B total or fundamental active power has

changed sign.

0x0 R/W

1 REVAPA Set this bit to enable an interrupt when the

Phase A total or fundamental active power has

changed sign.

0x0 R/W

0 EGYRDY Set this bit to enable an interrupt when the

power values in the xWATTHR, xVAHR xVARHR

xFWATTHR, xFVAHR, and xFVARHR registers

update, after EGY_TIME 8 kSPS samples or line

cycles, depending on the EGY_TMR_MODE bit in

the EP_CFG register.

0x0 R/W

Loading...

Loading...