ADE9000 Technical Reference Manual UG-1098

Rev. 0 | Page 73 of 86

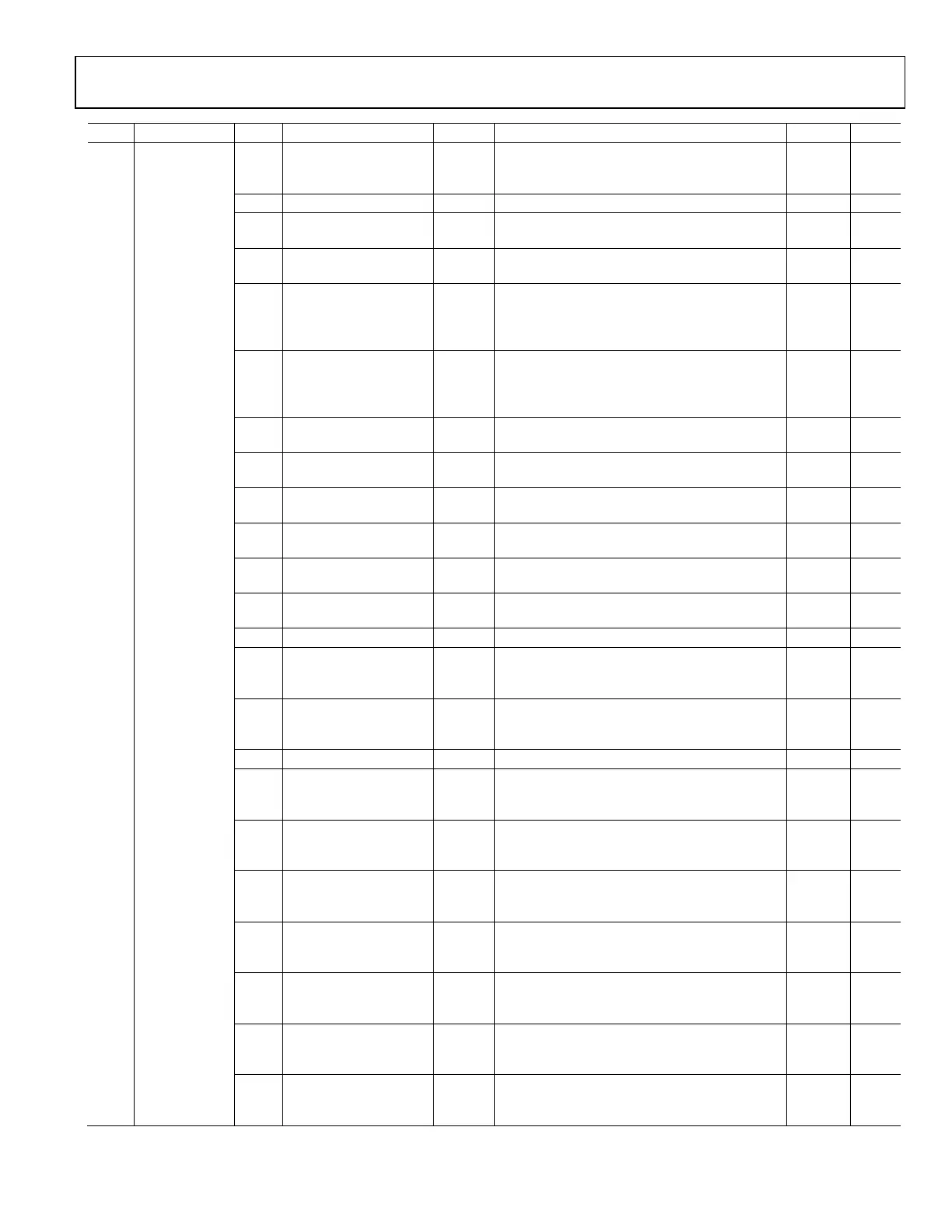

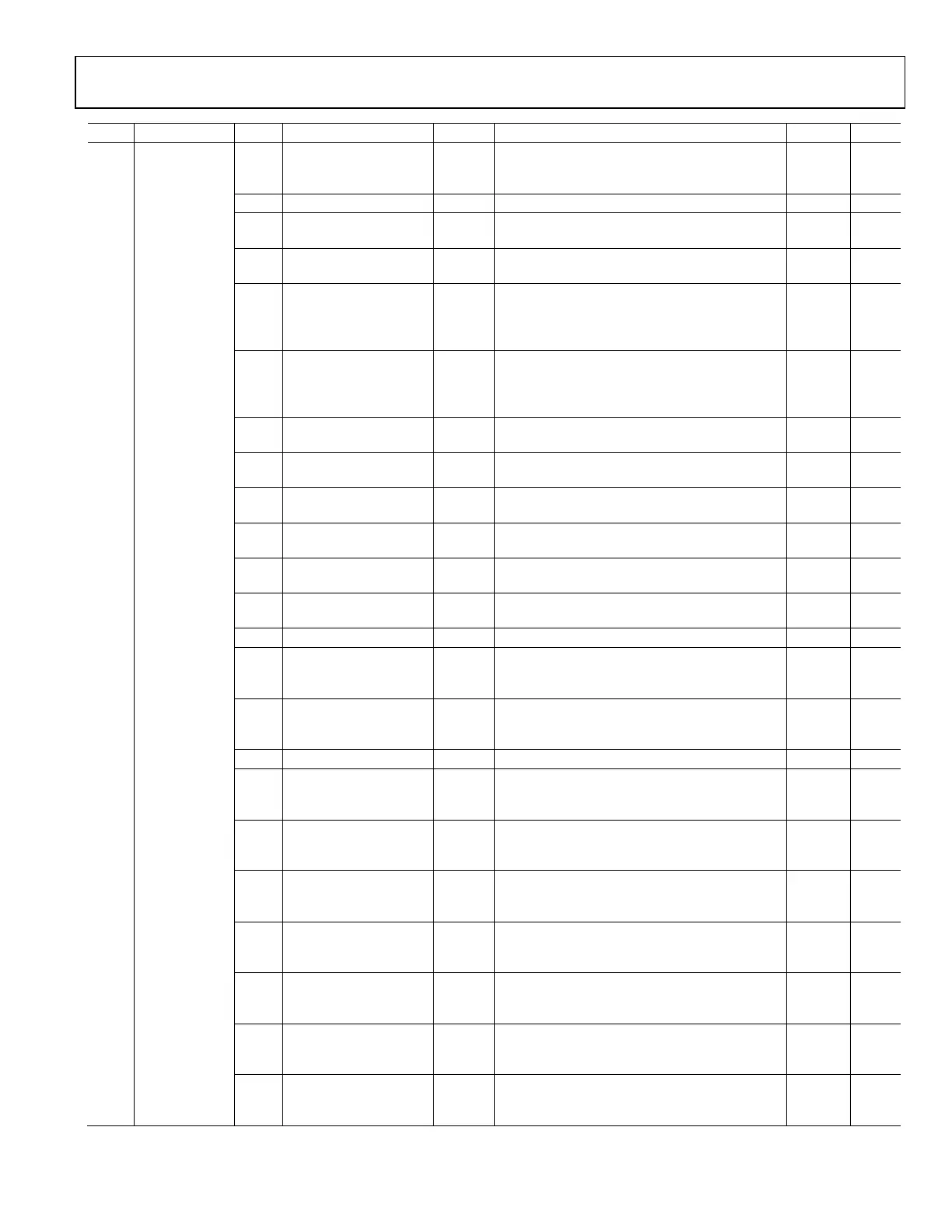

Addr. Name Bits Bit Name Settings Description Reset Access

0x406 MASK1 31 ERROR3 Set this bit to enable an interrupt if ERROR3 occurs.

Issue a software reset or hardware reset to clear

this error.

0x0 R/W

30 ERROR2 Set this bit to enable an interrupt if ERROR2 occurs. 0x0 R/W

This interrupt is not maskable. Issue a software

reset or hardware reset to clear this error.

28 ERROR0 This interrupt is not maskable. Issue a software

reset or hardware reset to clear this error.

0x0 R/W

27 CRC_DONE Set this bit to enable an interrupt when the

configuration register CRC calculation is complete,

after initiated by writing the FORCE_CRC_UPDATE

bit in the CRC_FORCE register.

0x0 R/W

26 CRC_CHG Set this bit to enable an interrupt if any of the

registers monitored by the configuration register

CRC change value. The CRC_RSLT register holds

the new configuration register CRC value.

0x0 R/W

25 DIPC Set this bit to enable an interrupt when the

Phase C voltage enters a dip condition

0x0 R/W

24 DIPB Set this bit to enable an interrupt when the

Phase B voltage enters a dip condition.

0x0 R/W

23 DIPA Set this bit to enable an interrupt when the

Phase A voltage enters a dip condition.

0x0 R/W

22 SWELLC Set this bit to enable an interrupt when the

Phase C voltage enters a swell condition.

0x0 R/W

21 SWELLB Set this bit to enable an interrupt when the

Phase B voltage enters a swell condition.

0x0 R/W

20 SWELLA Set this bit to enable an interrupt when the

Phase A voltage enters a swell condition.

0x0 R/W

19 RESERVED Reserved. 0x0 R

18 SEQERR Set this bit to enable an interrupt when on a

phase sequence error on the phase voltage

zero-crossings.

0x0 R/W

Set this bit to enable an interrupt when one of

the currents enabled in the OC_EN bits in the

CONFIG3 register enters an overcurrent condition.

16 RESERVED Reserved. 0x0 R

15 ZXIC Set this bit to enable an interrupt when a zero-

crossing is detected on the Phase C current

channel.

0x0 R/W

Set this bit to enable an interrupt when a zero-

crossing is detected on the Phase B current

channel.

13 ZXIA Set this bit to enable an interrupt when a zero-

crossing is detected on the Phase A current

channel.

0x0 R/W

12 ZXCOMB Set this bit to enable an interrupt when a zero-

crossing is detected on the combined signal

from VA, VB, and VC.

0x0 R/W

11 ZXVC Set this bit to enable an interrupt when a zero-

crossing is detected on the Phase C voltage

channel.

0x0 R/W

10 ZXVB Set this bit to enable an interrupt when a zero-

crossing is detected on the Phase B voltage

channel.

0x0 R/W

9 ZXVA Set this bit to enable an interrupt when a zero-

crossing is detected on the Phase A voltage

channel.

0x0 R/W

Loading...

Loading...