ADE9000 Technical Reference Manual UG-1098

Rev. 0 | Page 75 of 86

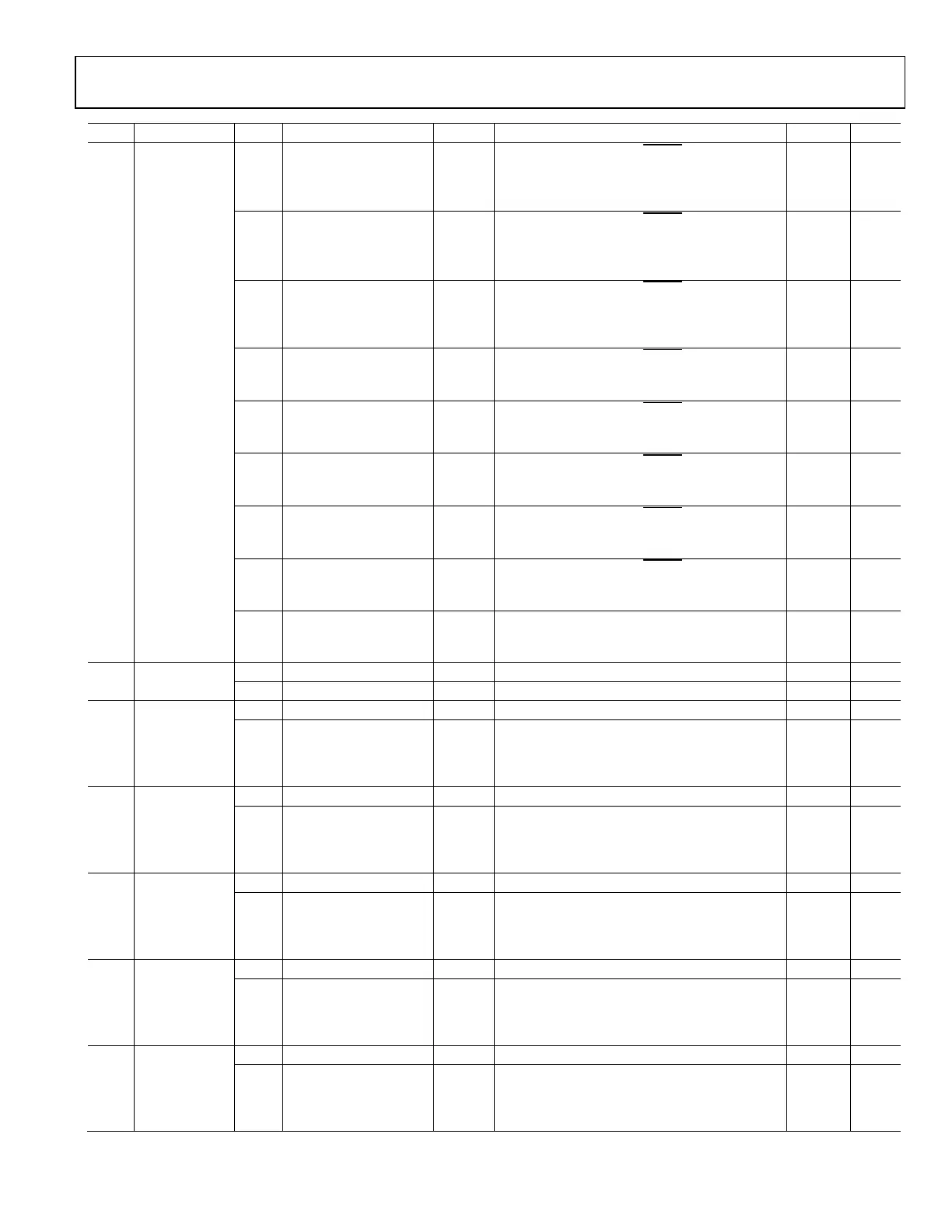

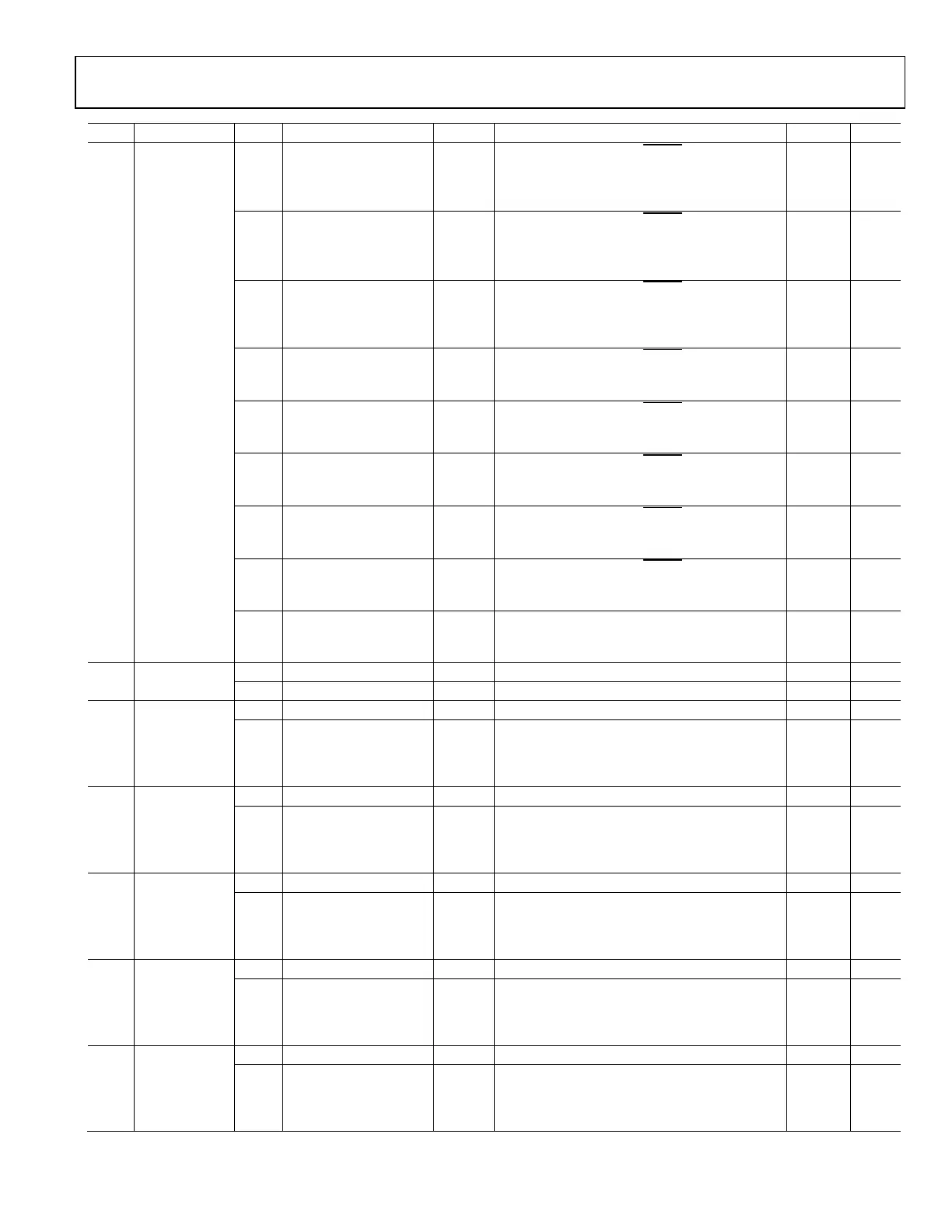

Addr. Name Bits Bit Name Settings Description Reset Access

Set this bit to enable the

EVENT

indicate if the last CF3 pulse was from negative

energy. This bit is updated when a CF3 pulse is

output, when the CF3 pin goes from high to low.

7 REVPSUM2 Set this bit to enable the

EVENT

pin to go low to

indicate if the last CF2 pulse was from negative

energy. This bit is updated when a CF2 pulse is

output, when the CF2 pin goes from high to low.

0x0 R/W

Set this bit to enable the

EVENT

indicate if the last CF1 pulse was from negative

energy. This bit is updated when a CF1 pulse is

output, when the CF1 pin goes from high to low.

5 SWELLCEN Set this bit to enable the

EVENT

pin to go low to

indicate that the Phase C voltage is in a swell

condition.

0x0 R/W

4 SWELLBEN Set this bit to enable the

EVENT

pin to go low to

indicate that the Phase B voltage is in a swell

condition.

0x0 R/W

3 SWELLAEN Set this bit to enable the

EVENT

pin to go low to

indicate that the Phase A voltage is in a swell

condition.

0x0 R/W

2 DIPCEN Set this bit to enable the

EVENT

pin to go low to

indicate that the Phase C voltage is in a dip

condition.

0x0 R/W

Set this bit to enable the

EVENT

indicate that the Phase B voltage is in a dip

condition.

0 DIPAEN Set this bit to enable the EVENT pin to go low to

indicate that the Phase A voltage is in a dip

condition.

0x0 R/W

0x409 OILVL [31:24] RESERVED Reserved. 0x0 R

[23:0] OILVL_VAL Over current detection threshold level. 0xFFFFFF R/W

0x40A OIA [31:24] RESERVED Reserved. 0x0 R

[23:0] OI_VAL Phase A overcurrent RMS½ value. If a phase is

enabled, with the OC_ENA bit set in the CONFIG3

register and AIRMSONE greater than the OILVL

threshold, this value is updated.

0x0 R

0x40B OIB [31:24] RESERVED Reserved. 0x0 R

[23:0] OIB_VAL Phase B overcurrent RMS½ value. If a phase is

enabled, with the OC_ENB bit set in the CONFIG3

register and BIRMSONE greater than the OILVL

threshold, this value is updated.

0x0 R

0x40C OIC [31:24] RESERVED Reserved. 0x0 R

[23:0] OIC_VAL Phase C overcurrent RMS½ value. If a phase is

enabled, with the OC_ENC bit set in the CONFIG3

register and CIRMSONE greater than the OILVL

threshold, this value is updated.

0x0 R

0x40D OIN [31:24] RESERVED Reserved. 0x0 R

[23:0] OIN_VAL Neutral current overcurrent RMS½ value. If

enabled, with the OC_ENN bit set in the CONFIG3

register and NIRMSONE greater than the OILVL

threshold, this value is updated.

0x0 R

0x40F VLEVEL [31:24] RESERVED Reserved. 0x0 R

[23:0] VLEVEL_VAL Register used in the algorithm that computes

the fundamental active, reactive, and apparent

powers, as well as the fundamental IRMS and VRMS

values.

0x45D45 R/W

Loading...

Loading...