55

8068C–AVR–06/08

XMEGA A3

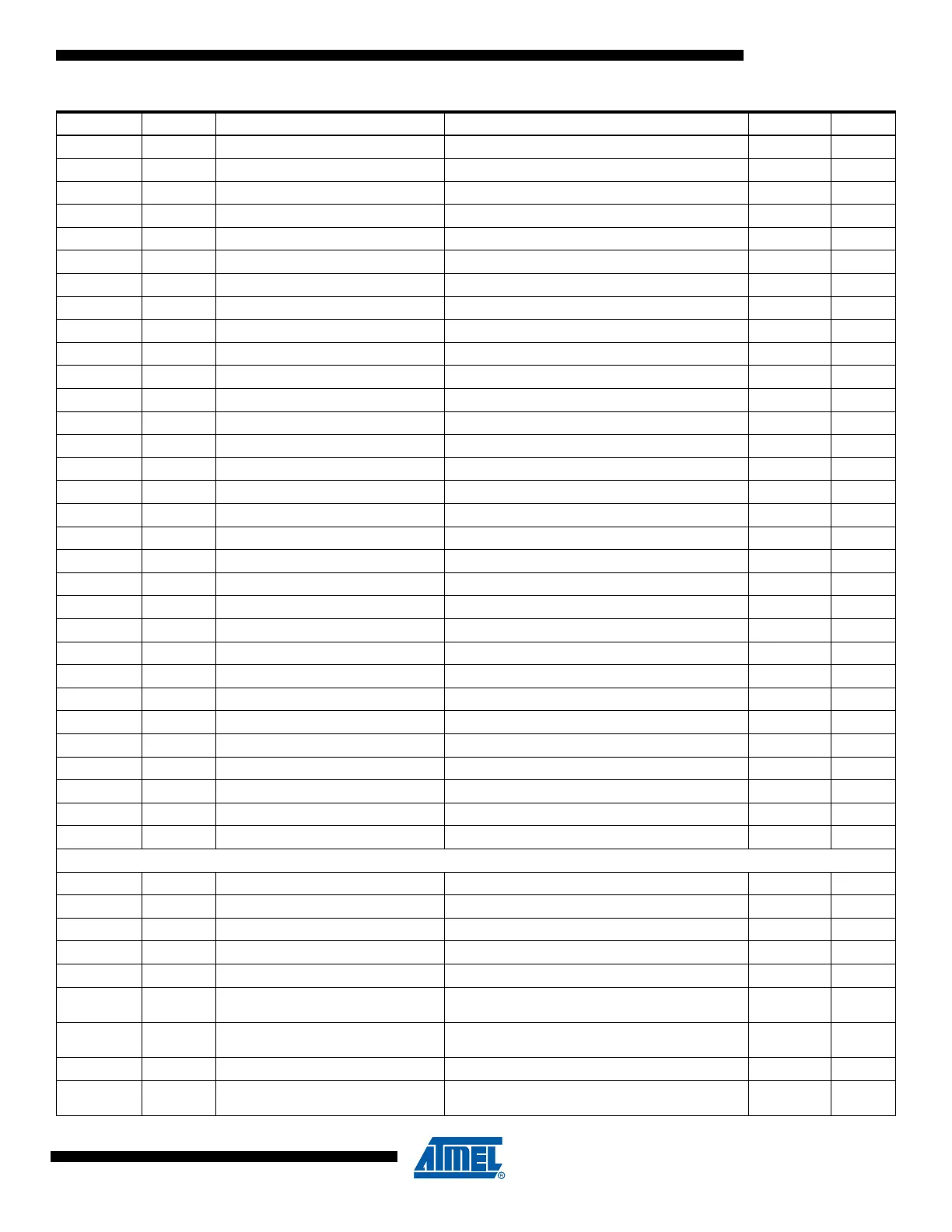

CALL k call Subroutine PC ← k None 3 / 4

(1)

RET Subroutine Return PC ← STACK None 4 / 5

(1)

RETI Interrupt Return PC ← STACK I 4 / 5

(1)

CPSE Rd,Rr Compare, Skip if Equal if (Rd = Rr) PC ← PC + 2 or 3 None 1 / 2 / 3

CP Rd,Rr Compare Rd - Rr Z,C,N,V,S,H 1

CPC Rd,Rr Compare with Carry Rd - Rr - C Z,C,N,V,S,H 1

CPI Rd,K Compare with Immediate Rd - K Z,C,N,V,S,H 1

SBRC Rr, b Skip if Bit in Register Cleared if (Rr(b) = 0) PC ← PC + 2 or 3 None 1 / 2 / 3

SBRS Rr, b Skip if Bit in Register Set if (Rr(b) = 1) PC ← PC + 2 or 3 None 1 / 2 / 3

SBIC A, b Skip if Bit in I/O Register Cleared if (I/O(A,b) = 0) PC ← PC + 2 or 3 None 2 / 3 / 4

SBIS A, b Skip if Bit in I/O Register Set If (I/O(A,b) =1) PC ← PC + 2 or 3 None 2 / 3 / 4

BRBS s, k Branch if Status Flag Set if (SREG(s) = 1) then PC ← PC + k + 1 None 1 / 2

BRBC s, k Branch if Status Flag Cleared if (SREG(s) = 0) then PC ← PC + k + 1 None 1 / 2

BREQ k Branch if Equal if (Z = 1) then PC ← PC + k + 1 None 1 / 2

BRNE k Branch if Not Equal if (Z = 0) then PC ← PC + k + 1 None 1 / 2

BRCS k Branch if Carry Set if (C = 1) then PC ← PC + k + 1 None 1 / 2

BRCC k Branch if Carry Cleared if (C = 0) then PC ← PC + k + 1 None 1 / 2

BRSH k Branch if Same or Higher if (C = 0) then PC ← PC + k + 1 None 1 / 2

BRLO k Branch if Lower if (C = 1) then PC ← PC + k + 1 None 1 / 2

BRMI k Branch if Minus if (N = 1) then PC ← PC + k + 1 None 1 / 2

BRPL k Branch if Plus if (N = 0) then PC ← PC + k + 1 None 1 / 2

BRGE k Branch if Greater or Equal, Signed if (N ⊕ V= 0) then PC ← PC + k + 1 None 1 / 2

BRLT k Branch if Less Than, Signed if (N ⊕ V= 1) then PC ← PC + k + 1 None 1 / 2

BRHS k Branch if Half Carry Flag Set if (H = 1) then PC ← PC + k + 1 None 1 / 2

BRHC k Branch if Half Carry Flag Cleared if (H = 0) then PC ← PC + k + 1 None 1 / 2

BRTS k Branch if T Flag Set if (T = 1) then PC ← PC + k + 1 None 1 / 2

BRTC k Branch if T Flag Cleared if (T = 0) then PC ← PC + k + 1 None 1 / 2

BRVS k Branch if Overflow Flag is Set if (V = 1) then PC ← PC + k + 1 None 1 / 2

BRVC k Branch if Overflow Flag is Cleared if (V = 0) then PC ← PC + k + 1 None 1 / 2

BRIE k Branch if Interrupt Enabled if (I = 1) then PC ← PC + k + 1 None 1 / 2

BRID k Branch if Interrupt Disabled if (I = 0) then PC ← PC + k + 1 None 1 / 2

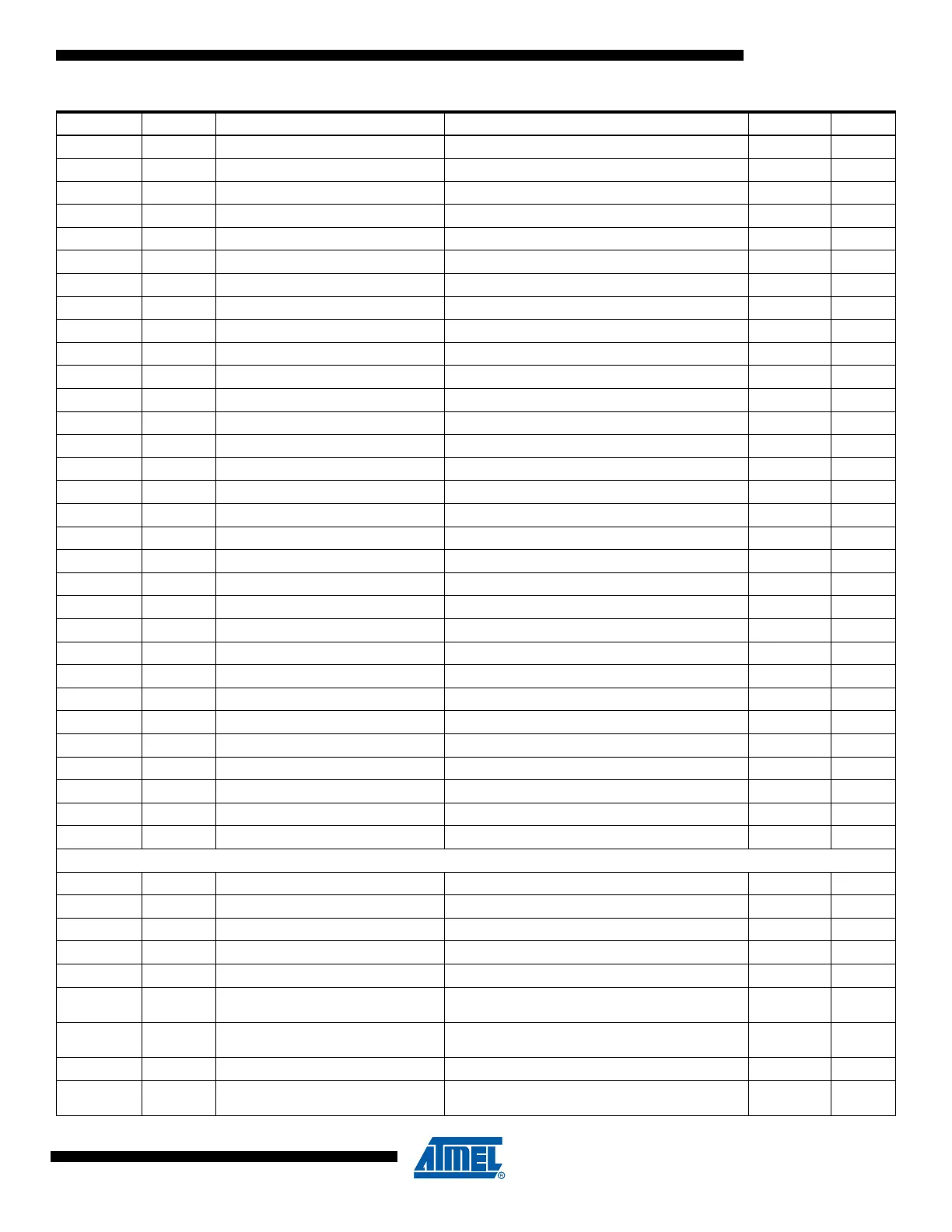

Data Transfer Instructions

MOV Rd, Rr Copy Register Rd ← Rr None 1

MOVW Rd, Rr Copy Register Pair Rd+1:Rd ← Rr+1:Rr None 1

LDI Rd, K Load Immediate Rd ← K None 1

LDS Rd, k Load Direct from data space Rd ← (k) None 2

(1)(2)

LD Rd, X Load Indirect Rd ← (X) None 1

(1)(2)

LD Rd, X+ Load Indirect and Post-Increment Rd

X

←

←

(X)

X + 1

None 1

(1)(2)

LD Rd, -X Load Indirect and Pre-Decrement X ← X - 1,

Rd ← (X)

←

←

X - 1

(X)

None 2

(1)(2)

LD Rd, Y Load Indirect Rd ← (Y) ← (Y) None 1

(1)(2)

LD Rd, Y+ Load Indirect and Post-Increment Rd

Y

←

←

(Y)

Y + 1

None 1

(1)(2)

Mnemonics Operands Description Operation Flags #Clocks

Loading...

Loading...