56

8068C–AVR–06/08

XMEGA A3

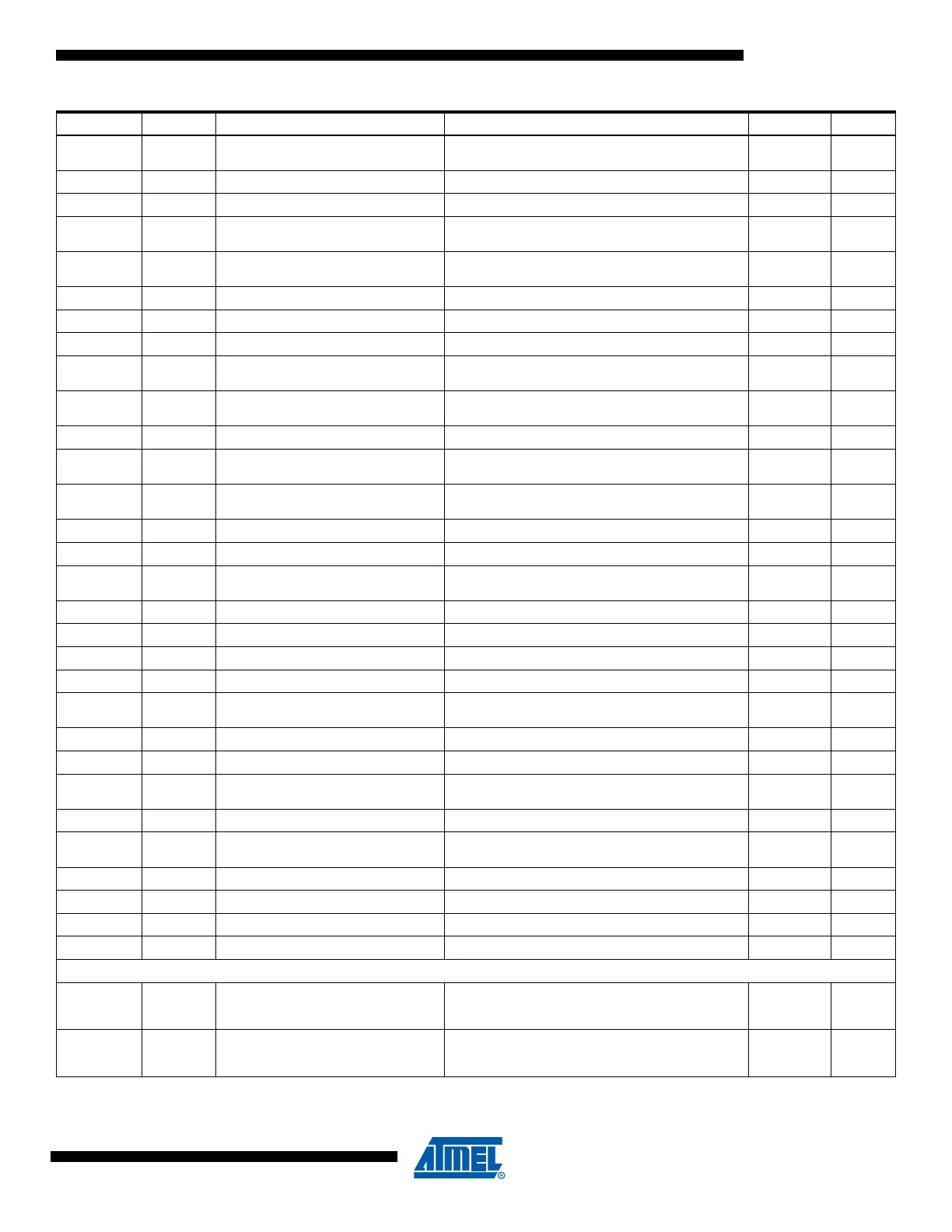

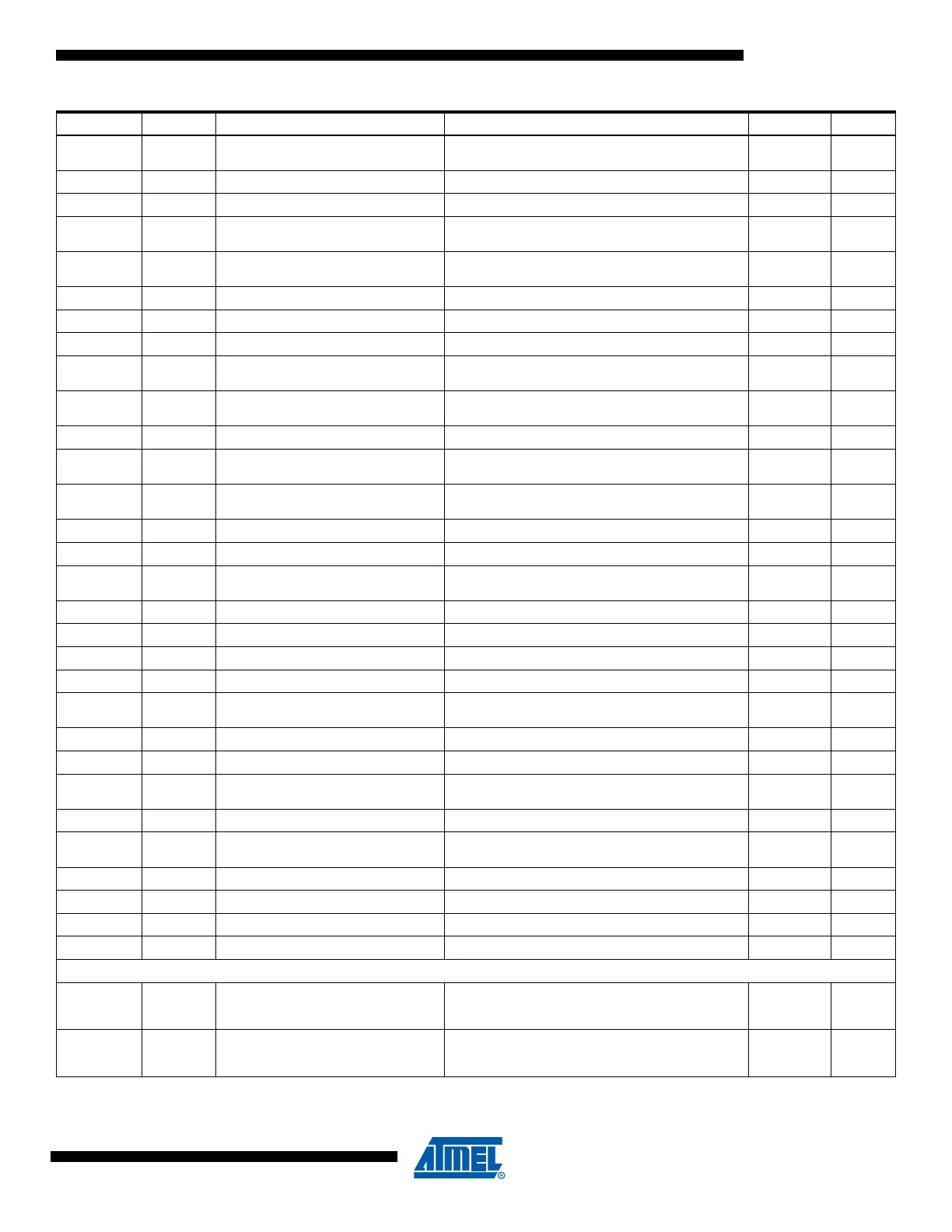

LD Rd, -Y Load Indirect and Pre-Decrement Y

Rd

←

←

Y - 1

(Y)

None 2

(1)(2)

LDD Rd, Y+q Load Indirect with Displacement Rd ← (Y + q) None 2

(1)(2)

LD Rd, Z Load Indirect Rd ← (Z) None 1

(1)(2)

LD Rd, Z+ Load Indirect and Post-Increment Rd

Z

←

←

(Z),

Z+1

None 1

(1)(2)

LD Rd, -Z Load Indirect and Pre-Decrement Z

Rd

←

←

Z - 1,

(Z)

None 2

(1)(2)

LDD Rd, Z+q Load Indirect with Displacement Rd ← (Z + q) None 2

(1)(2)

STS k, Rr Store Direct to Data Space (k) ← Rd None 2

(1)

ST X, Rr Store Indirect (X) ← Rr None 1

(1)

ST X+, Rr Store Indirect and Post-Increment (X)

X

←

←

Rr,

X + 1

None 1

(1)

ST -X, Rr Store Indirect and Pre-Decrement X

(X)

←

←

X - 1,

Rr

None 2

(1)

ST Y, Rr Store Indirect (Y) ← Rr None 1

(1)

ST Y+, Rr Store Indirect and Post-Increment (Y)

Y

←

←

Rr,

Y + 1

None 1

(1)

ST -Y, Rr Store Indirect and Pre-Decrement Y

(Y)

←

←

Y - 1,

Rr

None 2

(1)

STD Y+q, Rr Store Indirect with Displacement (Y + q) ← Rr None 2

(1)

ST Z, Rr Store Indirect (Z) ← Rr None 1

(1)

ST Z+, Rr Store Indirect and Post-Increment (Z)

Z

←

←

Rr

Z + 1

None 1

(1)

ST -Z, Rr Store Indirect and Pre-Decrement Z ← Z - 1 None 2

(1)

STD Z+q,Rr Store Indirect with Displacement (Z + q) ← Rr None 2

(1)

LPM Load Program Memory R0 ← (Z) None 3

LPM Rd, Z Load Program Memory Rd ← (Z) None 3

LPM Rd, Z+ Load Program Memory and Post-Increment Rd

Z

←

←

(Z),

Z + 1

None 3

ELPM Extended Load Program Memory R0 ← (RAMPZ:Z) None 3

ELPM Rd, Z Extended Load Program Memory Rd ← (RAMPZ:Z) None 3

ELPM Rd, Z+ Extended Load Program Memory and Post-

Increment

Rd

Z

←

←

(RAMPZ:Z),

Z + 1

None 3

SPM Store Program Memory (RAMPZ:Z) ← R1:R0 None -

SPM Z+ Store Program Memory and Post-Increment

by 2

(RAMPZ:Z)

Z

←

←

R1:R0,

Z + 2

None -

IN Rd, A In From I/O Location Rd ← I/O(A) None 1

OUT A, Rr Out To I/O Location I/O(A) ← Rr None 1

PUSH Rr Push Register on Stack STACK ← Rr None 1

(1)

POP Rd Pop Register from Stack Rd ← STACK None 2

(1)

Bit and Bit-test Instructions

LSL Rd Logical Shift Left Rd(n+1)

Rd(0)

C

←

←

←

Rd(n),

0,

Rd(7)

Z,C,N,V,H 1

LSR Rd Logical Shift Right Rd(n)

Rd(7)

C

←

←

←

Rd(n+1),

0,

Rd(0)

Z,C,N,V 1

Mnemonics Operands Description Operation Flags #Clocks

Loading...

Loading...