ASDA-A2 Chapter 8 Parameters

Revision February, 2017 8-41

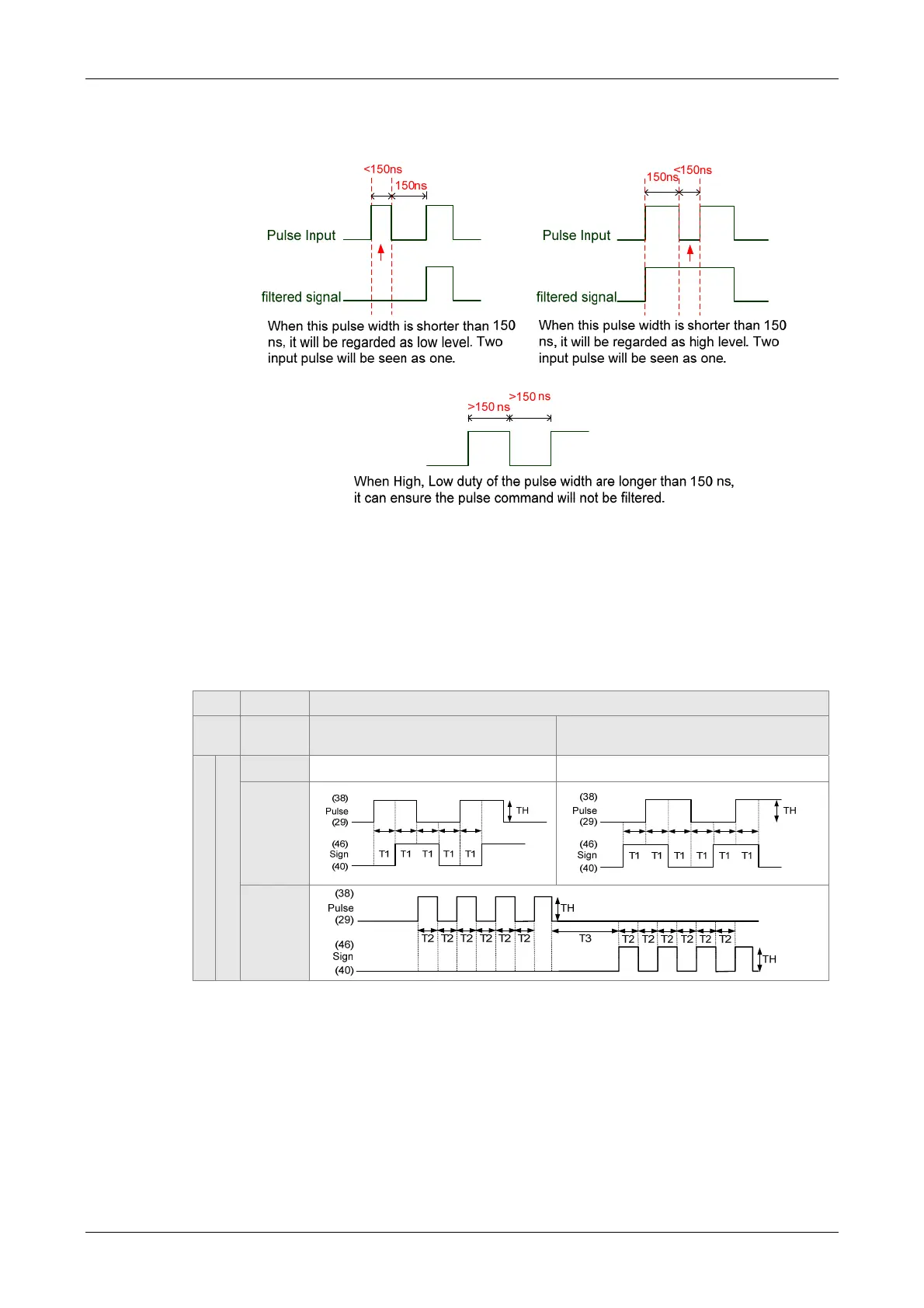

Note: When the source of external pulse is from the high-speed differential signal

and the setting value is 0 (the high-speed filter frequency is 3.33Mpps at the

moment), then:

If the user uses 2~4 MHz input pulse, it is suggested to set the filter value to 4.

Please note that the applicable version is: DSP version 1.036 sub05 and CPLD

version above 10.

Note: When the signal is the high-speed pulse specification of 4 Mpps and the

settings value of the filter is 4, then pulse will not be filtered.

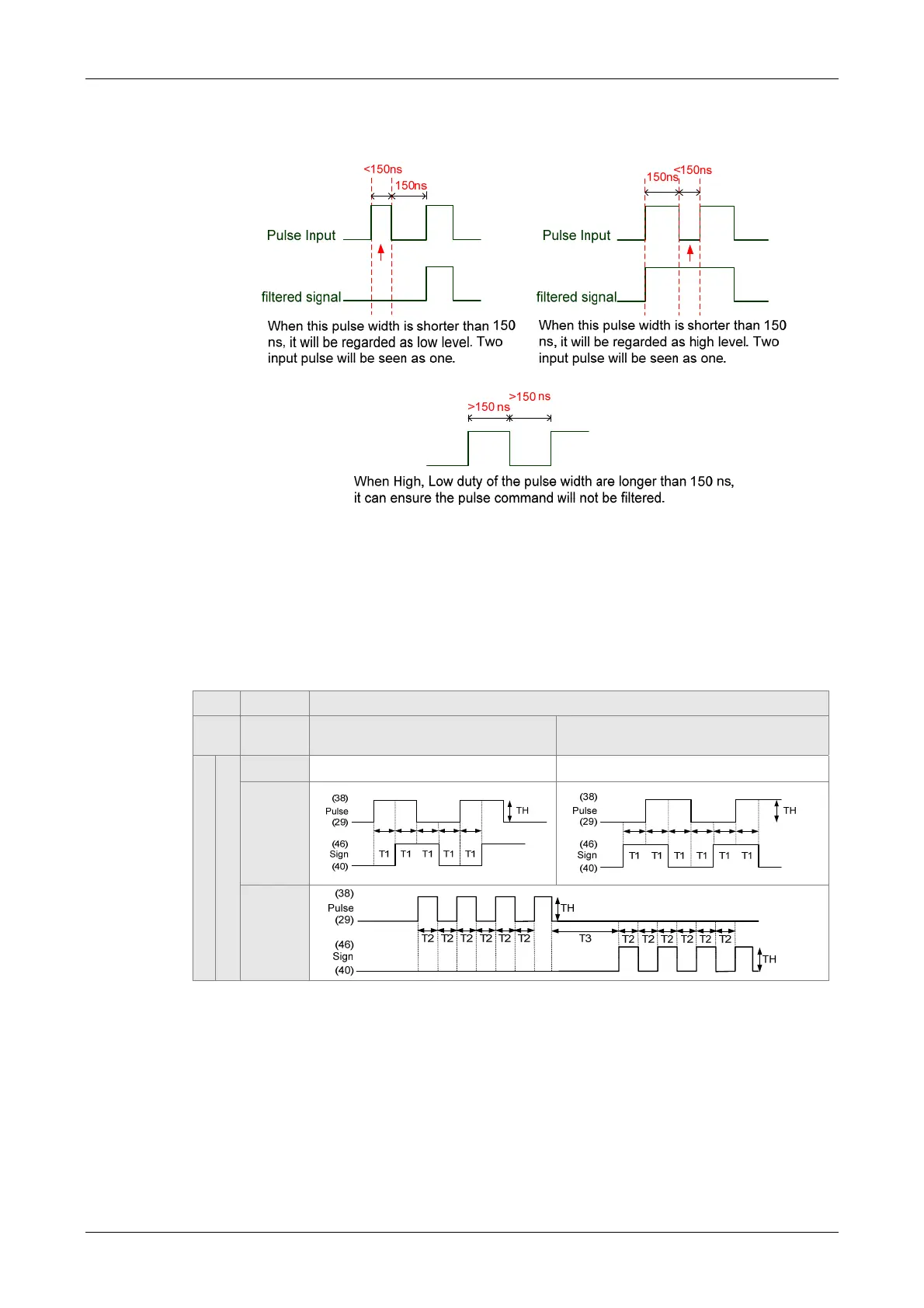

Logic Type

High-speed and Low-speed pulse input

Logic

Pulse

Type

Forward Reverse

0

Positive Logic

A Pulse Phase Lead A Pulse Phase Lag

AB phase

pulse

CW and

CCW

pulse

Loading...

Loading...