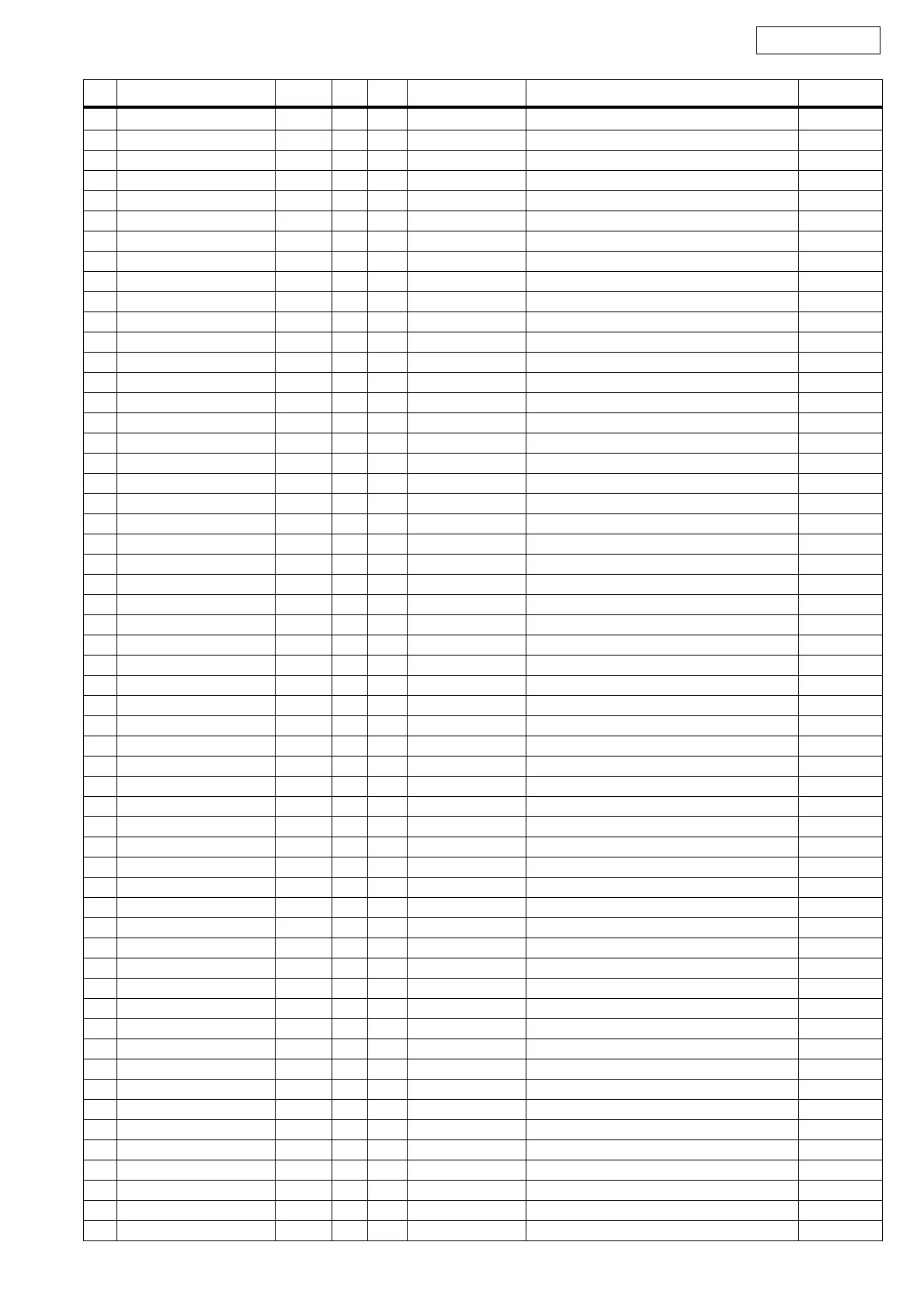

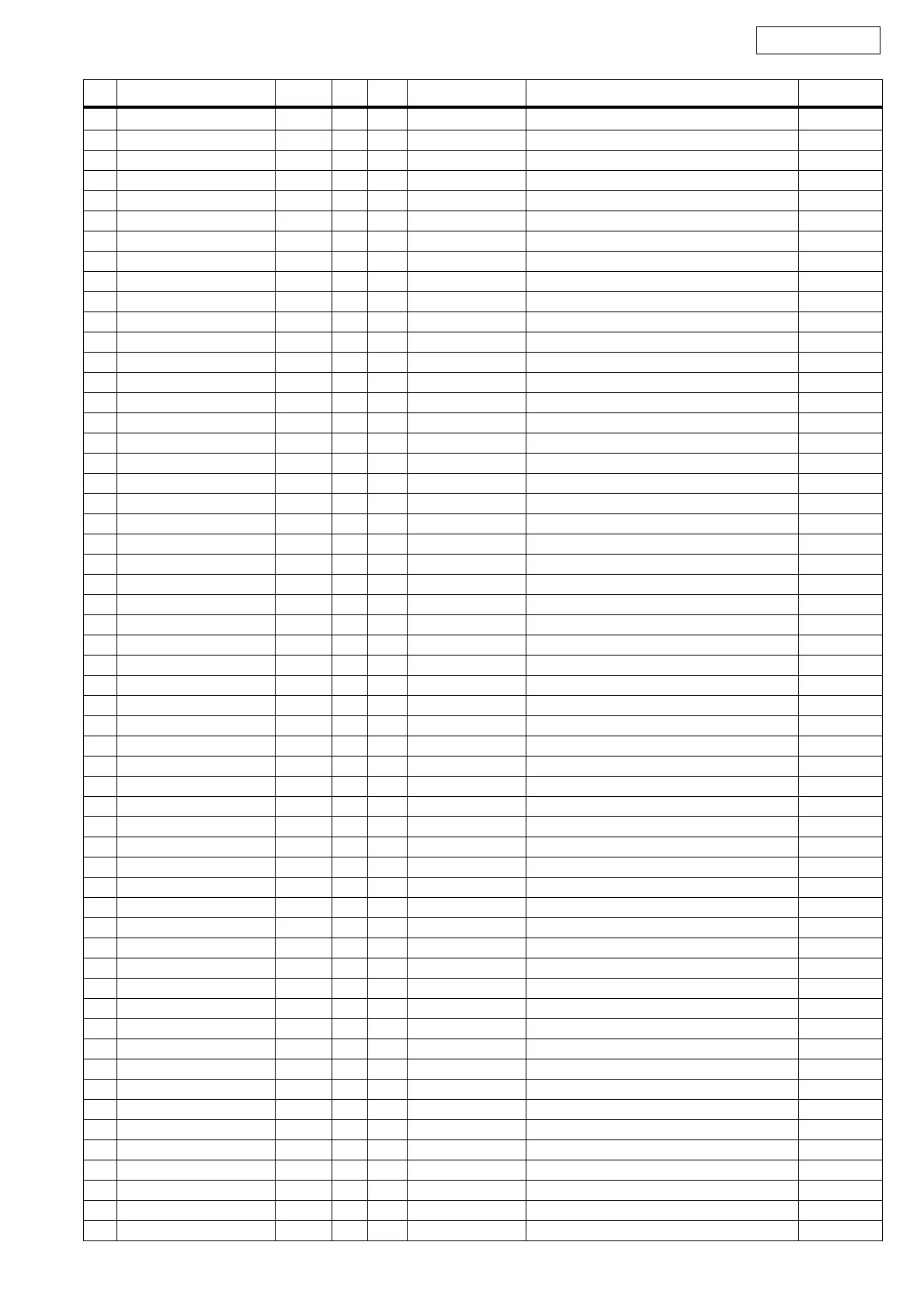

31

DCD-1500AE

32

P73/CTS2

~

/RTS2~/TA1IN/V

~

P73 O H XMSLAT SERIAL DATA LATCH for CXD2753R

33 P72/CLK2/TA1OUT/V CLK2 O H MSCK SERIAL DATA CLK for CXD2753R

34 P71/RXD2/SCL/TA0IN/TB5IN RXD2 I MSDATAO SERIAL DATA INPUT from CXD2753R PULL UP

35 P70/TXD2/SDA/TA0OUT TXD2 O H MSDATAI SERIAL DATA OUTPUT for CXD2753R PULL UP

36 P67/TXD1 TXD1 O H CD_LED WRITE USE (22k P.U)

Flash(w:pull up)

37 VCC VCC

38 P66/RXD1 RXD1 I H SA_LED WRITE USE (22k P.U)

Flash(w:pull up)

39 VSS VSS

40 P65/CLK1 P65 I H PULL_DWN 5.1K PULL DOWN(NON CONECT)

Flash(w:pull down)

41

P64/CTS1~/RTS1~/CTS0~/CLKS1

P64 O H DRVRST RESET for CXD1885Q(RESET=L)

Flash(w:pull up)

42 P63/TXD0 TXD0 O H DRVRX SERIAL DATA for CXD1885Q

43 P62/RXD0 RXD0 I DRVTX SERIAL DATA from CXD1885Q

44 P61/CLK0 CLK0 O H DRVCLK DATA CLOCK for CXD1885Q

45 P60/CTS0~/RTS0~ CTS0~ I DRVRDY DATA READY SIGNAL from CXD1885Q

46 P13_7 O OPEN New AL Test3

47 P13_6 O OPEN New AL Test4

48 P13_5 O OPEN New AL Test5

49 P13_4 O L CD_SEL INTERNAL CD PLAY ONLT "H" (RESERVE)

50 P57/RDY~/CLKOUT P57 I MRDY READY from CXD1885Q (NOT USE)

51 P56/ALE P56 I OPEN1 OPEN(anytime)

Flash(w:pull up)

52 P55/HOLD~ P55 I P_UP2 10K PULL UP(NON CONECT) Flash(w:GND)

53 P54/HLDA~ P54 I OPEN2 OPEN(must)

54 P13_3 O H OPEN DSPMOSI

55 P13_2 I (L) OPEN DSPMISO

56 P13_1 O L OPEN DSPSPICLK

57 P13_0 O H OPEN DSPSPICS

58 P53/BCLK P53 - OPEN3 OPEN(must)

59 P52/RD~ P52 I MRD READ STROBE for CXD1885Q(NOT USE)

60 P51/WRH~/BHE~ P51 I OPEN4 OPEN(must)

61 P50/WRL~/WR~ P50 I MWR WRITE STROBE for CXD1885Q(NOT USE)

Flash(w:pull up)

62 P12_7 I (L) OPEN BUSYEPROM

63 P12_6 O H OPEN VPP

64 P12_5 O L OPEN ROMRST

65 P47/CS3~ CS3~ O H MCS CHIP SELECT for CXD1885Q

66 P46/CS2~ P46 O H CLS_DRV TRAY CLOSE DRIVE CONTROL

67 P45/CS1~ P45 O H OPN_DRV TRAY OPEN DRIVE CONTROL

68 P44/CS0~ CS2~ O H MCS2 CHIP SELECT for 1M-SRAM

69 P43/A19 P43 O L OPEN OPEN

70 P42/A18 P42 O L OPEN OPEN

71 P41/A17 P41 O L OPEN OPEN

72 P40/A16 A16 O A16 ADRRES LINE

73 P37/A15 A15 O A15 ADRRES LINE

74 P36/A14 A14 O A14 ADRRES LINE

75 P35/A13 A13 O A13 ADRRES LINE

76 P34/A12 A12 O A12 ADRRES LINE

77 P33/A11 A11 O A11 ADRRES LINE

78 P32/A10 A10 O A10 ADRRES LINE

79 P31/A9 A9 O A9 ADRRES LINE

80 P12_4 O L OPEN SEL4fs

81 P12_3 O L OPEN RST3

82 P12_2 O H D_OUT SPDIF SIGNAL LINE ON/OFF H: OUTPUT

83 P12_1 O L OPEN OPEN

84 P12_0 O L OPEN OPEN

85 VCC VCC - --- 3.3V

86 P30/A8(/-/D7) A8 O A8 ADRRES LINE

87 VSS VSS - --- GND

pin port

function

I/O

Initial

mode action NOTE

Loading...

Loading...