Cinterion

®

Java Terminals Hardware Interface Description

8.4 Configuration via I

2

C Interface

69

EHSxT_BGS5T_HID_v02 2014-05-23

Confidential / Preliminary

Page 67 of 70

Possible result codes for status command (see Section 8.4.1.3 and above Table 25):

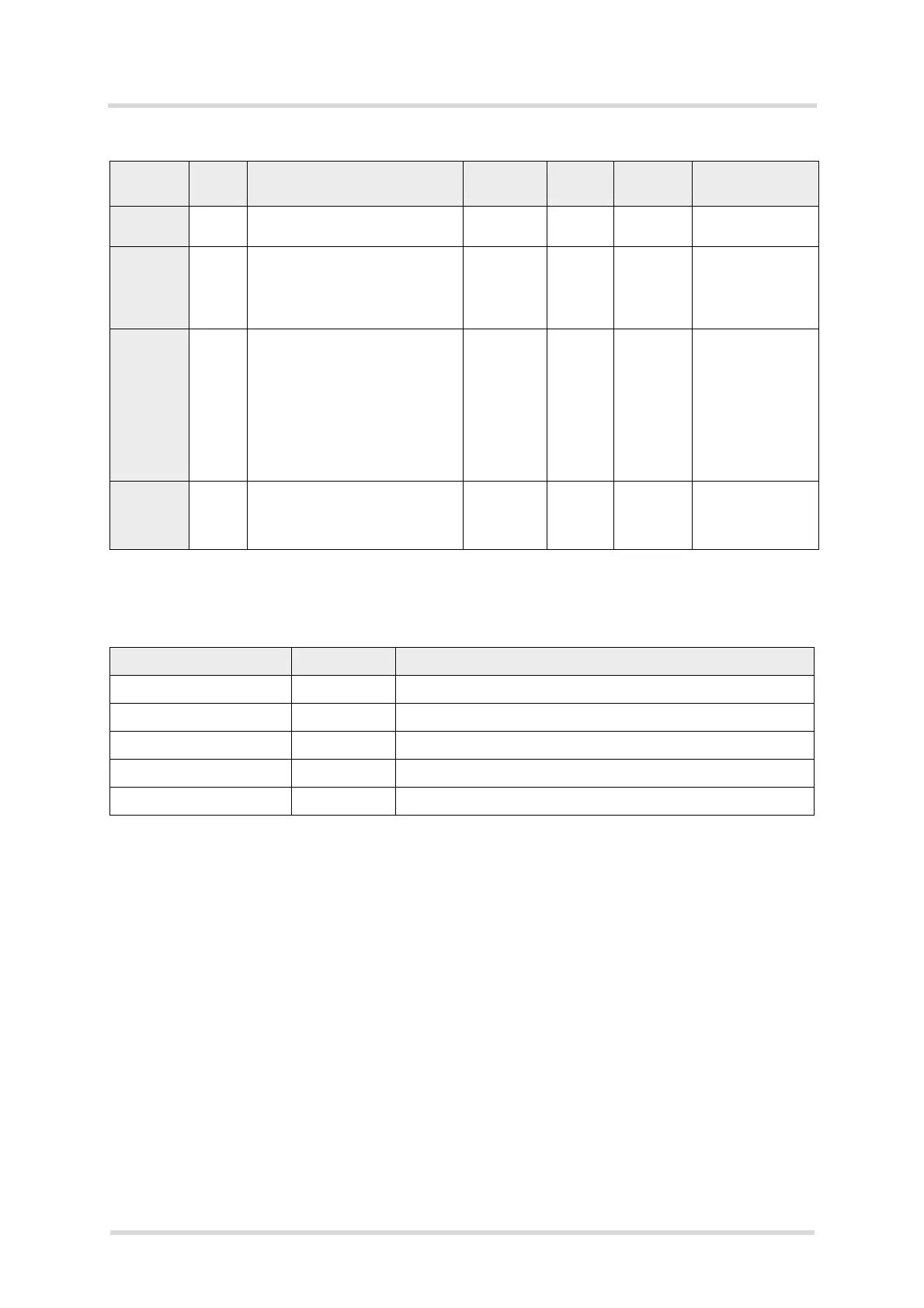

0x50 R/W ADC1_IN/DSR0 ADCDSRR Yes 0x00 0: Analog In

1: Digital Out

0x80 W Trigger delay. Specifies delay

time for a reset. If a trigger delay

time is specified, the watchdog is

prevented from resetting the

module for the given time.

TDR No 0x00 Set time in min-

utes.

1...255: Minutes

0: Disable

0xFD R Hardware watchdog‘s firmware

version

VER -- [0x00..0x99]

[MAJ MIN]

4:MSB: MAJ

4:LSB: MIN

MAJ: Main release

number (e.g., 1.x)

MIN: Sub release

number (e.g., x.0)

as in version v1.0

0xFF W Read address register (RAR) RAR No 0x00 0x00..0xFF

Only valid

addresses contain

valid values

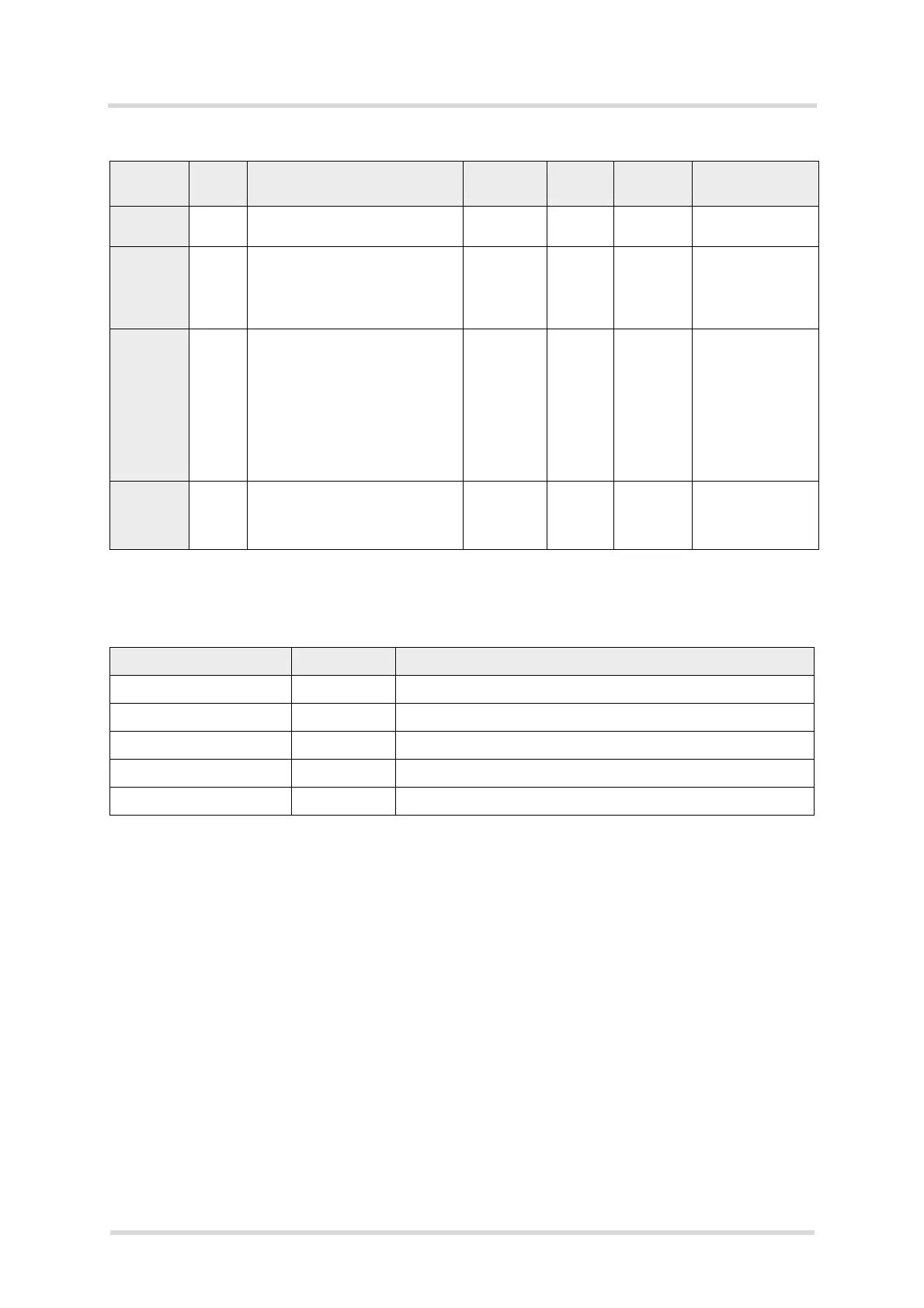

Table 26: I

2

C status result codes

Result Code Comment

OK 0x00 Last command was executed successfully

PROTOCOL_ERROR 0x01 Protocol error, i.e. wrong number of bytes

ILLEGAL_ADDRESS 0x02 Illegal register address

ILLEGAL_ARGUMENT 0x03 Illegal argument. Argument is out of allowed range.

UNDEFINED 0xFF

Table 25: Address register for I

2

C commands

Register

address

Read/

Write

Description Name Non-

volatile

Default Value range

Loading...

Loading...