- 25 -

Hardware Installation

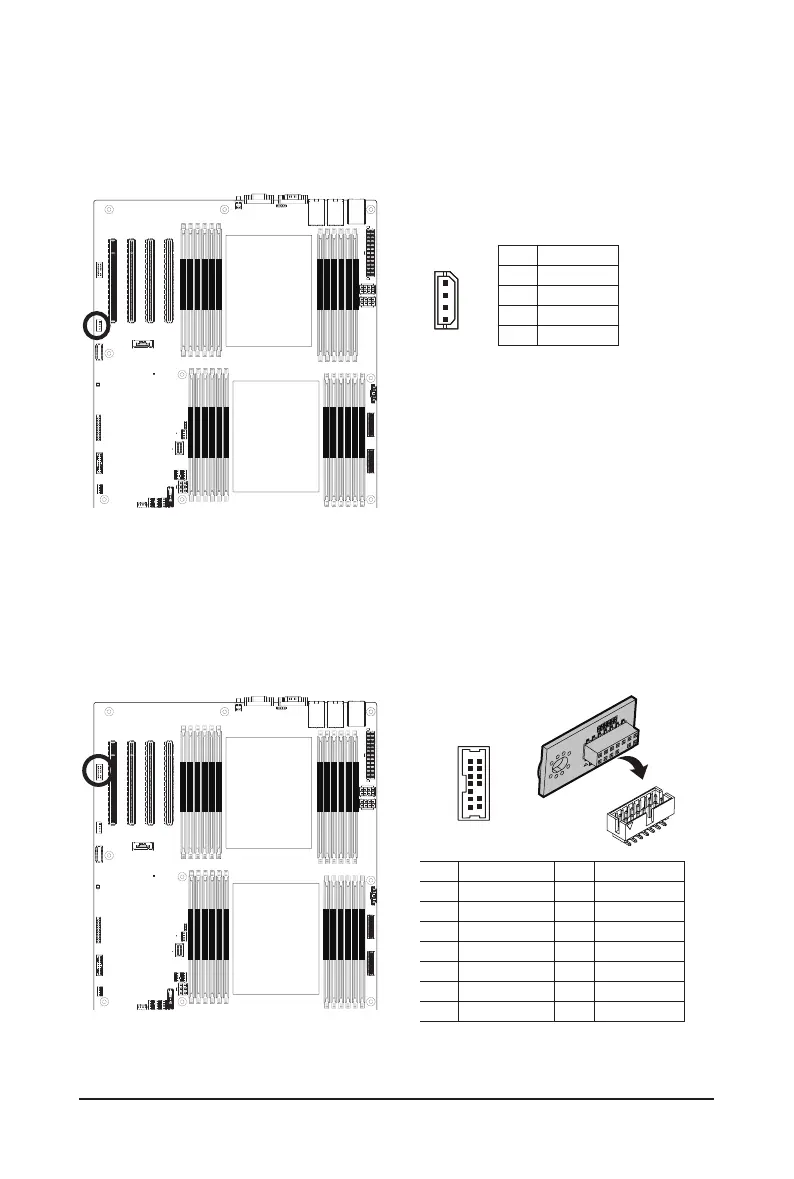

CPU1

CPU0

DIMM_P1_Q1

DIMM_P1_N0

DIMM_P1_M0

DIMM_P1_P0

DIMM_P1_O0

DIMM_P1_R0

DIMM_P1_T0

DIMM_P1_W0

DIMM_P1_X0

DIMM_P1_U0

DIMM_P1_V0

DIMM_P1_S0

DIMM_P0_B0

DIMM_P0_E0

DIMM_P0_F0

DIMM_P0_C0

DIMM_P0_D0

DIMM_P0_A0

DIMM_P0_K0

DIMM_P0_H0

DIMM_P0_G0

DIMM_P0_J0

DIMM_P0_I0

DIMM_P0_L 0

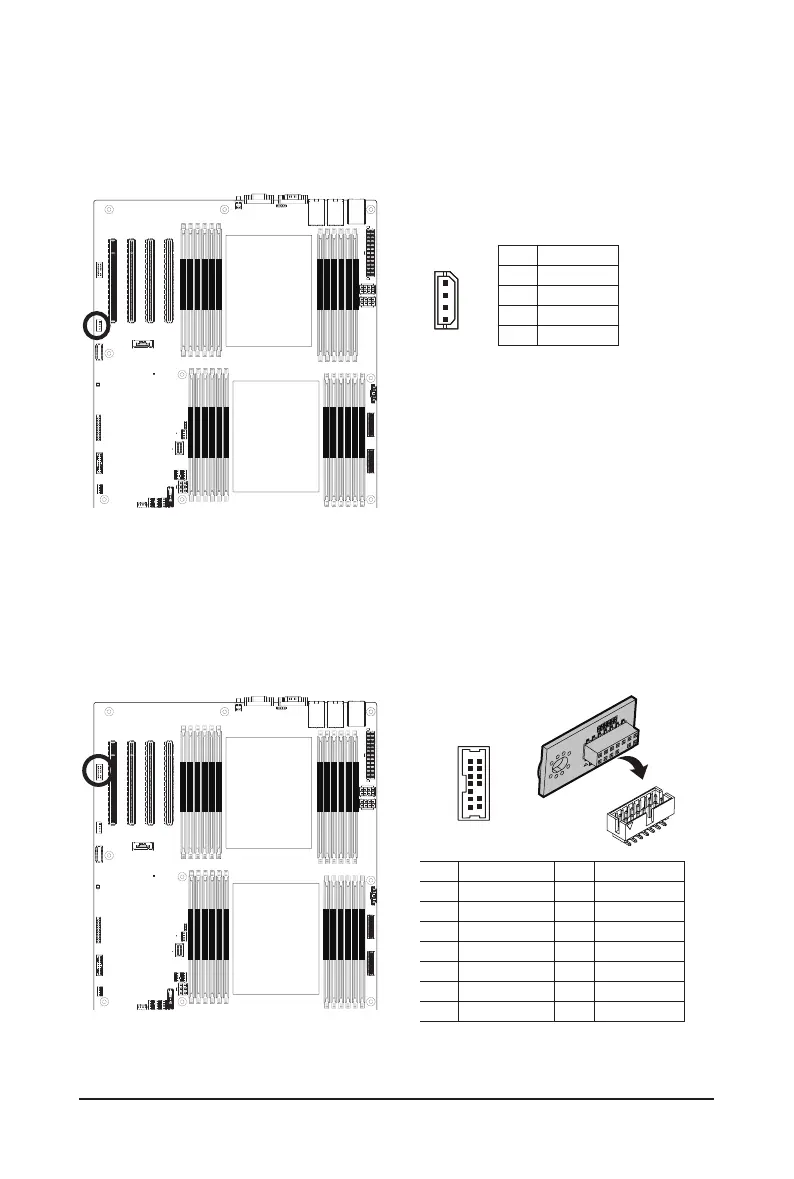

18) IPMB (Intelligent Platform Management Bus) Connector

The Intelligent Platform Management Bus Communications Protocol defines a byte-level transport for

transferringIntelligentPlatformManagementInterfaceSpecication(IPMI)messagesbetweenintelligentI2C

devices.

Pin No. Denition

1 Clock

2 GND

3 Data

4 VCC

CPU1

CPU0

DIMM_P1_Q1

DIMM_P1_N0

DIMM_P1_M0

DIMM_P1_P0

DIMM_P1_O0

DIMM_P1_R0

DIMM_P1_T0

DIMM_P1_W0

DIMM_P1_X0

DIMM_P1_U0

DIMM_P1_V0

DIMM_P1_S0

DIMM_P0_B0

DIMM_P0_E0

DIMM_P0_F0

DIMM_P0_C0

DIMM_P0_D0

DIMM_P0_A0

DIMM_P0_K0

DIMM_P0_H0

DIMM_P0_G0

DIMM_P0_J0

DIMM_P0_I0

DIMM_P0_L 0

19) SPI_TPM (Trusted Platform Module Connector)

Trusted Platform Module (TPM) is an international standard for a secure cryptoprocessor, a dedicated

microcontroller designed to secure hardware through integrated cryptographic keys.

Pin No. Denition Pin No. Denition

1 Clock 8 NC

2 P_3V3_AUX 9 NC

3 LPC_RST 10 No Pin

4 NC 11 NC

5 SPI_MISO 12 GND

6 IRQ_SPI 13 SPI_CS_N

7 SPI_MOSI 14 GND

1

4

Loading...

Loading...