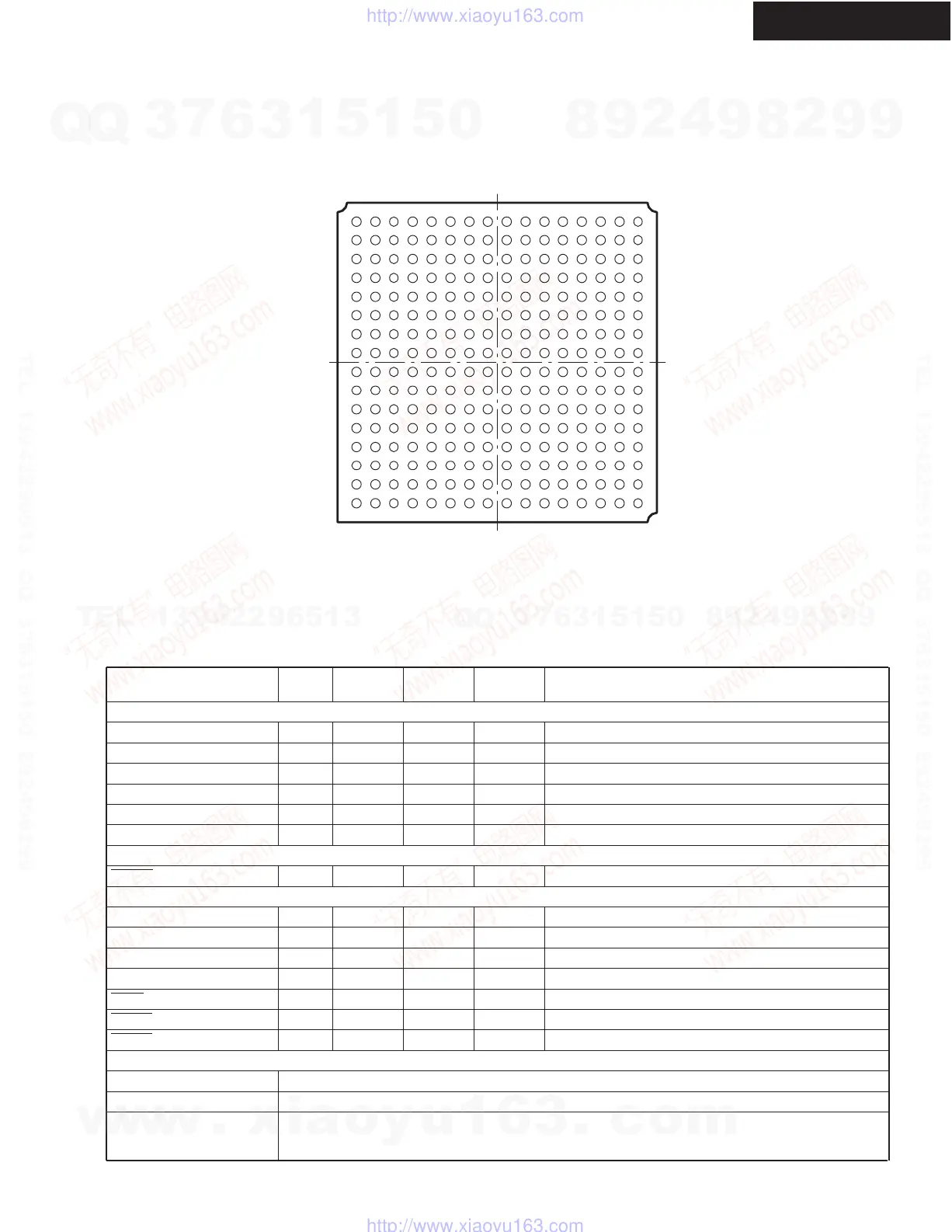

PIN CONFIGURATION(2/2)

IC BLOCK DIAGRAMS AND TERMINAL DESCRIPTIONS -17

Q3401, Q3501: D790E001BZDH300 (Audio DSP)

TX-SR806/SA806

Bottom View

13

24

5

68

79

10

11

14

15

12

13

16

N

A

C

B

D

F

E

L

G

H

J

K

M

P

T

R

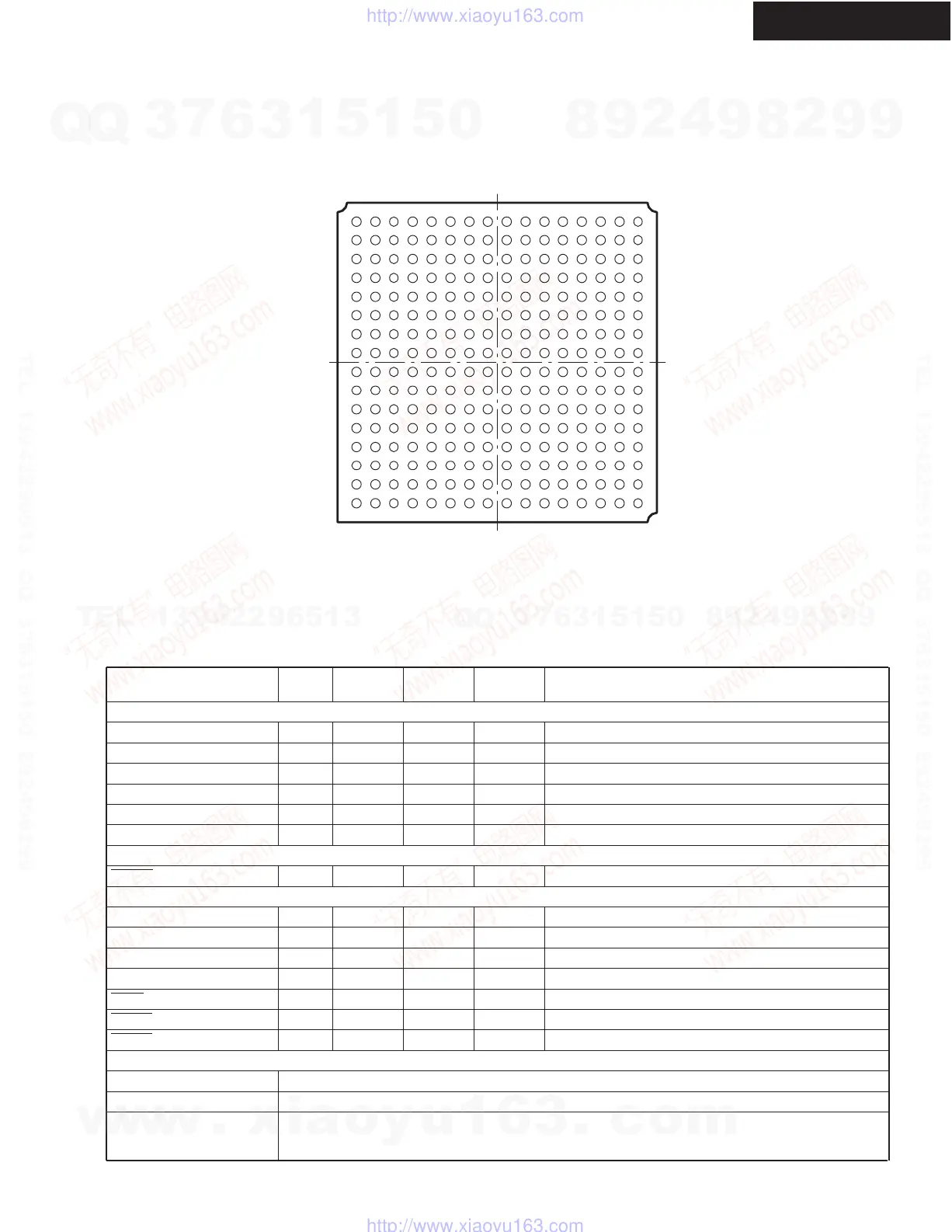

TERMINAL DESCRIPTION(1/5)

BALL

SIGNAL NAME TYPE

(1)

PULL

(2)

GPIO

(3)

DESCRIPTION

NO.

Clocks

OSCIN J2 I - N 1.2-V Oscillator Input

OSCOUT J3 O - N 1.2-V Oscillator Output

OSCV

DD

J4 PWR - N Oscillator 1.2-V V

DD

tap point (for filter only)

OSCV

SS

J1 PWR - N Oscillator V

SS

tap point (for filter only)

CLKIN H2 I - N Alternate clock input (3.3-V LVCMOS Input)

PLLHV K2 PWR - N PLL 3.3-V Supply Input (requires external filter)

Device Reset

RESET G2 I - N Device reset pin

Emulation/JTAG Port

TCK P1 I IPU N Test Clock

TMS K3 I IPU N Test Mode Select

TDI L1 I IPU N Test Data In

TDO M2 OZ IPU N Test Data Out

TRST K4 I IPD N Test Reset

EMU[0] M1 IO IPU N Emulation Pin 0

EMU[1]

N1 IO IPU N Emulation Pin 1

Power Pins

Core Supply (CV

DD

) E6, E7, E8, E9, E10, E11, G5, G12, H5, H12, J5, J12, K5, K12, M6, M7, M8, M9, M10, M11

IO Supply (DV

DD

) A2, A15, B1, B16, D4, D5, D12, D13, E4, E13, J14, M4, M13, N5, N12, P8, R1, R16, T2, T15

A1, A7, A10, A16, E5, E12, F5, F6, F7, F8, F9, F10, F11, F12, G1, G6, G7, G8, G9, G10, G11, G16, H3,

Ground (V

SS

) H6, H7, H8, H9, H10, H11, J6, J7, J8, J9, J10, J11, K1, K6, K7, K8, K9, K10, K11, K16, L5, L6, L7, L8, L9,

L10, L11, L12, M5, M12, T1, T7, T10, T16

w

w

w

.

x

i

a

o

y

u

1

6

3

.

c

o

m

Q

Q

3

7

6

3

1

5

1

5

0

9

9

2

8

9

4

2

9

8

T

E

L

1

3

9

4

2

2

9

6

5

1

3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299

http://www.xiaoyu163.com

http://www.xiaoyu163.com

Loading...

Loading...